## D4.2 FRACTAL low-power services

| Deliverable Id:           | D4.2                              |

|---------------------------|-----------------------------------|

| Deliverable name:         | FRACTAL low-power services        |

| Status:                   | Draft                             |

| Dissemination level:      | PUBLIC                            |

| Due date of deliverable:  | 2022-10-31 (M26)                  |

| Actual submission date:   | 2022-10-25                        |

| Work package:             | WP4 "Safety, Security & Low Power |

|                           | Techniques"                       |

| Organization name of lead | ROT                               |

| contractor for this       |                                   |

| deliverable:              |                                   |

| Authors:                  | Nadia Caterina Zullo Lasala, ROT  |

|                           | Damiano Vallocchia, ROT           |

|                           | Amal Alrish, ROT                  |

|                           | Daniel Onwuchekwa, SIEG           |

|                           | Pascal Muoka, SIEG                |

|                           | Juan Garcia, QUA                  |

|                           | Ankur Raj, QUA                    |

|                           | Berkay Enginoglu, PLC2            |

|                           | Alexander Flick, PLC2             |

|                           | Luca Bertaccini, ETHZ             |

|                           | Leticia Pascual, SML              |

|                           | Raúl García, SML                  |

| Reviewers:                | Pietro Abbatangelo, MODIS         |

|                           | Frank K. Gürkaynak, ETHZ          |

#### Abstract:

The goal of WP4 is to develop safety, security, and low-power techniques for individual FRACTAL nodes. In T4.1 we investigated low-power services in seven components implemented in the FRACTAL project, and this document will report the results of this work, extending the preliminary implementations reported in D4.1. The development includes both the node level (i.e., individual FRACTAL nodes) as well as the system level (i.e., distributed systems comprised of FRACTAL nodes) in accordance with the FRACTAL system architecture.

|         | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 877056

Co-funded by the Horizon 2020 Programme of the European Union under grant agreement No 877056.

| Copyright © FRACTAL Project Consortium | 2 of 80 |

|----------------------------------------|---------|

|                                        |         |

|         | Project   | FRACTAL                    |  |  |

|---------|-----------|----------------------------|--|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |  |

|         | Del. Code | D4.2                       |  |  |

## Content

| 1       | His | story | <i>.</i>                                                                     |

|---------|-----|-------|------------------------------------------------------------------------------|

| 2       | Su  | Imm   | ary 6                                                                        |

| 3       | In  | trodu | uction                                                                       |

|         | 3.1 | Do    | ocument Organization11                                                       |

| 4       | Hig | gh-L  | evel Picture12                                                               |

|         | 4.1 | Da    | ata Compression for low power services13                                     |

|         | 4.2 | HA    | ATMA14                                                                       |

|         | 4.3 | Lo    | w Power services for PULP systems15                                          |

|         | 4.4 | Ve    | ersal RPU access for Power Services16                                        |

|         | 4.5 | Ag    | reement Protocol for Low-Power Services17                                    |

|         | 4.6 | Ve    | ersal Isolation Design- Functional Safety18                                  |

| 5       | Da  | ata C | compression for Low-Power Services - WP4T41-01 - ROT                         |

|         | 5.1 | LZ    | W compression technique19                                                    |

|         | 5.2 | De    | esign and implementation24                                                   |

|         | 5.3 | Те    | sting and evaluation26                                                       |

|         | 5.3 | 3.1   | Integration into UC627                                                       |

| 6<br>02 |     |       | chical Adaptive Time-triggered Multi-core Architecture (HATMA) - WP4T41-<br> |

|         | 6.1 | HA    | ATMA Subcomponents                                                           |

|         | 6.3 | 1.1   | Hierarchical Interactive Consistency Protocol (HICP)                         |

|         | 6.2 | De    | esign and implementation                                                     |

|         | 6.2 | 2.1   | Context Monitor (CM)31                                                       |

|         | 6.2 | 2.2   | Context Agreement Unit (CAU)32                                               |

|         | 6.3 | Те    | sting and evaluation35                                                       |

|         | 6.3 | 3.1   | Integration in UC8                                                           |

| 7       | Lo  | w-Pc  | ower Services for PULP Systems - WP4T41-03 - ETH                             |

|         | 7.1 | Со    | omponent description                                                         |

|         | 7.2 | De    | esign and implementation                                                     |

|         | 7.3 | Те    | sting and evaluation40                                                       |

|         | 7.: | 3.1   | Integration into UC340                                                       |

| 8       | Ve  | ersal | RPU Access for Power Services - WP4T41-04 - PLC242                           |

|         | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

| 8  | 8.1               | Con   | nponent description42                                     |  |  |

|----|-------------------|-------|-----------------------------------------------------------|--|--|

| 8  | 3.2               | Des   | ign and implementation42                                  |  |  |

| 8  | 8.3               | Tes   | ting and evaluation43                                     |  |  |

| 9  | Agre              | eem   | ent Protocol for Low-Power Services – WP4T41-05 - QUA44   |  |  |

| 9  | 0.1               | Con   | nponent description44                                     |  |  |

| 9  | .2                | Des   | ign and implementation44                                  |  |  |

|    | 9.2.              | 1     | Master selection45                                        |  |  |

|    | 9.2.              | 2     | Synchronization of slaves45                               |  |  |

| 9  | .3                | Tes   | ting and evaluation46                                     |  |  |

| 10 | Vers              | sal I | solation Design- Functional Safety - WP4T41-06 - PLC2     |  |  |

| 1  | 0.1               | С     | component description                                     |  |  |

| 1  | 0.2               | D     | esign and implementation49                                |  |  |

|    | 10.2              | 2.1   | Hardware Block Design and Settings49                      |  |  |

|    | 10.2              | 2.2   | Software Platform51                                       |  |  |

| 1  | 0.3               | Т     | esting and evaluation52                                   |  |  |

|    | 10.3              | 3.1   | Integration into UC852                                    |  |  |

| 11 | Vali              | datio | on of LEDEL library for low-Power Services - SML          |  |  |

| 1  | 1.1               | II    | ntroduction53                                             |  |  |

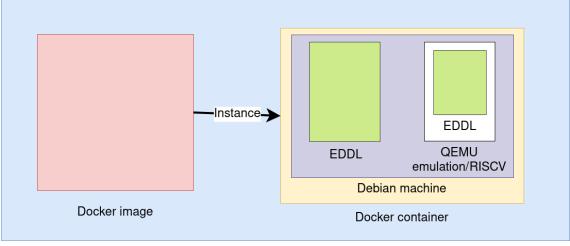

| 1  | 1.2               | E     | DDL code compilation process54                            |  |  |

|    | 11.2              | 2.1   | Code compilation for training and ONNX file creation54    |  |  |

|    | 11.2              | 2.2   | Example with RISC-V58                                     |  |  |

|    | 11.2              | 2.3   | Loading ONNX and inference process in the FRACTAL node59  |  |  |

|    | 11.2              | 2.4   | Importing ONNX file generated by PyTorch and TensorFlow63 |  |  |

|    | 11.2              | 2.5   | Cross-Compilation68                                       |  |  |

|    | 11.2              | 2.6   | Use Case 15 from DeepHealth project70                     |  |  |

| 12 | Con               | clus  | ions75                                                    |  |  |

| 13 | Bibl              | iogra | aphy76                                                    |  |  |

| 14 | List of figures77 |       |                                                           |  |  |

| 15 | List              | of ta | ables                                                     |  |  |

| 16 | List              | of A  | bbreviations80                                            |  |  |

| 2551243 | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

# 1 History

| Version | Date       | Modification reason                                         | Modified by  |

|---------|------------|-------------------------------------------------------------|--------------|

| 0.1     | 2022-05-31 | First contributions                                         | All partners |

| 0.2     | 2022-07-15 | Refine contributions and outline tests                      | All partners |

| 1.0     | 2022-07-20 | Draft version                                               | All partners |

| 2.0     | 2022-08-01 | New organization of the contents of the document            | All partners |

| 3.0     | 2022-09-06 | Major contributions to all chapters                         | All partners |

| 4.0     | 2022-09-20 | Addressing HLAB feedbacks, final contributions              | All partners |

| 5.0     | 2022-10-07 | Pre-final version of the document ready for internal review | ROT          |

| Final   | 2022-10-24 | Final version of the document ready for submission          | ROT          |

| Copyright © FRACTAL Project Consortium | 5 of 80 |

|----------------------------------------|---------|

|                                        |         |

| 2552253 | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

## 2 **Summary**

This deliverable aims to report the outcomes of T4.1 on Low-Power services. The results of the implementations carried out in the task are presented according to the components developed, which reflect the objectives of the task.

Namely, the work in T4.1 was focused on suitable Data Compression techniques for low-power services, specifically the LZW compression techniques, described in Section 5 (ROT). Moreover, this Task developed a hierarchical architecture to facilitate low-power services for FRACTAL systems with a time-triggered Network-on-Chip, with the work on the Hierarchical Adaptive Time-triggered Multi-core Architecture (HATMA), which will be described in Section 6 (SIEG). In addition, energy measurement and energy-efficient computing for low-power services for PULP systems have been explored in Section 7 (ETH). The task also investigated low-power communication protocols for a wireless network, in the Agreement Protocol in Chapter 9 (QUA). Furthermore, RPU based access for Power Services on safety focused Versal platforms have been explored in Sections 8 and 10 (PLC2) respectively. Finally, following the outcomes of WP3, T4.1 validated the adaptation of the LEDEL Library for low-power services in Section 11 (SML).

| Copyright © FRACTAL Project Consortium | 6 of 80 |

|----------------------------------------|---------|

|                                        |         |

| FRACTAL | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

|         | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

# 3 Introduction

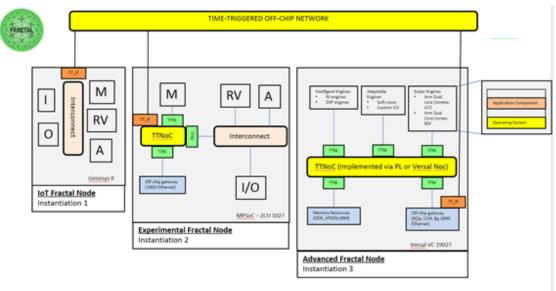

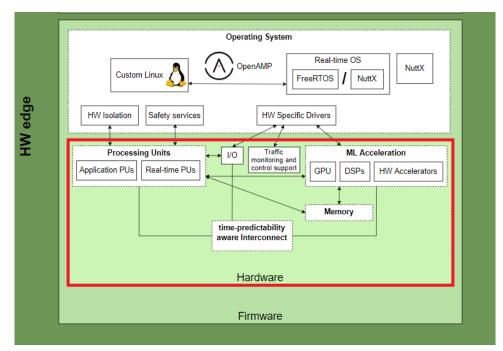

The goal of the 4<sup>th</sup> work package is to develop safety, security, and low-power services for individual FRACTAL nodes. In this document, we will shed light upon lowpower services for FRACTAL systems extending their preliminary implementations reported in the deliverable D4.1. The development includes both the node level (i.e., individual FRACTAL nodes) as well as the system level (i.e., distributed systems comprised of FRACTAL nodes) in accordance with the Fractal system architecture depicted in Figure 1. To this aim, we will provide low-power services for multi-core chips that use a time-triggered Network-On-Chip (NoC) to interconnect heterogeneous types of computing resources such as general-purpose processor cores. Moreover, we are developing low-power services for the interconnected FRACTAL nodes based on a hierarchical system concept with wire-bound and wireless time-triggered off-chip networks. Furthermore, we will extend the low-power services realized on FRACTAL nodes to the system level by investigating low-power communication protocols for wireless and wired networks. In addition, we will investigate new aggregation and compression algorithms to reduce the amount of time and data needed to transmit information over a channel. Finally, the validation process of LEDEL, the library to implement Machine Learning algorithms as a lowpower service, is detailed in accordance with the results of WP3.

I = Input, O = output, RV = Risc V, A = Accelerator, M = Memory, TTNI = Time-triggered Network Interface, TTNoC = Time-triggered Network-on-chip

Figure 1 Fractal system architecture

The strategic objective of this task is to guarantee the energy efficiency of the FRACTAL system. To achieve this objective, the task was realized by several building blocks/components which contribute to fulfill the T4.1 objectives and are reusable and could be demodulated by any use case (UC).

| Copyright © FRACTAL Project Consortium | 7 of 80 |

|----------------------------------------|---------|

|                                        |         |

| FRACTAL | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

|         | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

A brief description of each of the T4.1 components and how they contribute in achieving the Task objectives are reported in Table 1.

Table 1 Brief description of the components and contribution T4.1 objectives

| Data Compressio                                     | n for low-Power Services - WP4T41-01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description                                         | It is a data compression technique for low-power devices<br>applied at the system level. In particular, it is a software librar<br>developed in C++ which performs operations of data<br>compression and decompression making use of the universa<br>lossless data compression algorithm LZW.                                                                                                                                                                                                                                           |

| Contribution to<br>achieving the<br>T4.1 objectives |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HATMA - WP4T4:                                      | 1-02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Description                                         | It is a Hierarchical Adaptive Time-triggered Multi-con<br>Architecture used to facilitate services at the differen<br>hierarchies. It delivers adaptation services in a distributed<br>system of multiple nodes and within the nodes.                                                                                                                                                                                                                                                                                                   |

| Contribution to<br>achieving the<br>T4.1 objectives | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Low Power servic                                    | es for PULP systems - WP4T41-03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

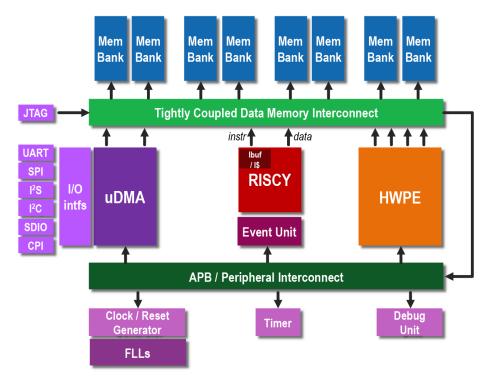

| Description                                         | It aims to enhance existing platforms to increase energy<br>efficiency and provide low-power FRACTAL services<br>Specifically, microarchitectural modifications and extensions to<br>the RISC-V platform are explored to specialize the architectura<br>for a specific application scenario, thus increasing its energy<br>efficiency. Additional components can be placed in differen<br>power domains, which can be powered down during the sleep<br>mode of the IoT device. Different power gating granularitie<br>are investigated. |

|                                                     | Copyright © FRACTAL Project Consortium 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FRACTAL | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

|         | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

| Contribution to<br>achieving the<br>T4.1 objectives | The component satisfies the objective of the task by exploring<br>fine-grained power gating and increasing the energy-efficiency<br>of the platform through microarchitectural modifications and<br>specialized architectures                                                                                                                                                                                                                                                         |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Versal RPU access                                   | for Power Services - WP4T41-04                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Description                                         | The component enhances the safety-centric Versal platform to<br>provide access to power control and monitoring services<br>through underlying HW accesses as provided by Versal<br>Isolation Design. This service proxy code is running on the real<br>time processing units (RPU) in the Versal processing system.<br>The mission mode (FRACTAL node) services use this<br>component along the provided protocol to retrieve a predefined<br>set of control and monitoring features. |

| Contribution to<br>achieving the<br>T4.1 objectives | This component offers power control and status monitoring for<br>the Versal FRACTAL node by setting the power domains,<br>Dynamic Voltage and Frequency Scaling (DVFS), and clock<br>gating. This provides the Versal-based low-power services and<br>so enables the physical node adaptivity for the HATMA services.                                                                                                                                                                 |

| Agreement Protoco                                   | ol for Low-Power Services - WP4T41-05                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

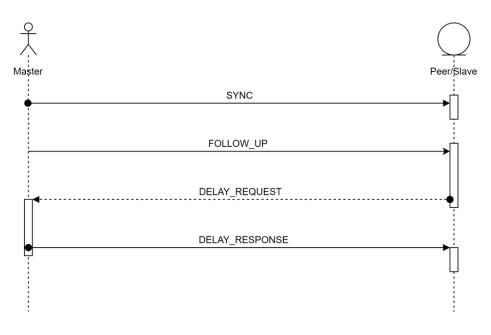

| Description                                         | It is an implementation of the agreement protocol on a wireless<br>network on low-power devices. This protocol aims at having<br>clock synchronization among all the devices connected in the<br>network.                                                                                                                                                                                                                                                                             |

| Contribution to<br>achieving the<br>T4.1 objectives | The component fulfills the T4.1 objective of investigation for<br>the low-powered wireless communication protocol, it helps in<br>providing a method for time-based synchronization on low-<br>powered devices. The synchronization is based on a PTP-like<br>method with low-powered microcontrollers sending<br>synchronization messages wirelessly. The implementation was<br>achieved using ESP-32 microcontrollers and a communication<br>protocol known as ESP-NOW.             |

| Versal Isolation De                                 | esign- Functional Safety - WP4T41-06                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Description                                         | It aims to enhance the common Versal platform to strictly<br>separate functional accesses and services from underlying HW<br>access. In particular, in safety augmented designs on the<br>Versal platform, the direct access to the infrastructure features<br>of given hardware is limited to a non-mission mode compute<br>core (RPU). This component exposes the actual internal state                                                                                             |

| FRACTAL | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

|         | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

|                                                     | to the mission mode (FRACTAL node) services in a way that<br>still allows to adhere to safety regulations. In addition, it<br>provides monitor services.                                                                                                                                                                             |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contribution to<br>achieving the<br>T4.1 objectives | This component defines the Versal FRACTAL node power<br>control and monitoring accesses that are available to the time-<br>triggered control instance. In safety-centric platforms, the<br>power control and monitoring features defined in this<br>component are only accessible through "Versal RPU access for<br>Power Services". |

Additionally, several activities have been carried out. In particular,

- In T4.1, the Data Compression for low-power services (WP4T41-01) has been designed and implemented. In addition, the effectiveness of this technique has been proven to evaluate this component.

- HATMA has been designed and implemented in hardware based on an NoC multi-core architecture. Runtime adaptation to slack events has been demonstrated while balancing a trade-off between adaptability overhead and energy saving.

- An agreement protocol was also developed in T4.1 for low-powered devices (WP4T41-05), here a wireless time-based synchronization was achieved with multiple microcontrollers. A PTP-like synchronization method was developed, which has one master and several slave devices. Additionally, a master selection routine was created for this task. This routine program is responsible for selecting a master device after the bootup process of all the peer devices. In case the master device loses its connection with the network, necessary fallback methods were also created to accommodate the selection of a new master device.

- Verification and validation of the LEDEL library have been carried out. They show that the LEDEL library can be used to implement neural network algorithms, compiled or exported to ONNX files, and then transfer to the FRACTAL node. Even more, programs created using PyTorch that define a neural network that can be exported to ONNX file can be as well transferred into the FRACTAL node, loaded using LEDEL, and perfectly executed.

- ETH investigated hardware specialization and microarchitectural modifications to increase the energy of PULP-based energy efficiency. Furthermore, ETH explored fine-grained power gating to minimize the power consumption powering off unused hardware units and allowing tuning the hardware configuration for specific application scenarios.

- For the Versal based platform the specific controls and monitoring of infrastructure features have been validated and checked against requirements to demonstrate scalability of a FRACTAL node. This informed the derived Versal power service components that have been developed with safety and isolation as a particular design constraint.

| FRACTAL | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

|         | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

## **3.1 Document Organization**

The document is organized as follows: in Section 4 we present a high-level picture of the Fractal solutions developed in WP4. Then, we report the detailed description, design and implementation, and evaluation and testing of data Compression for Low-Power Services, HATMA, low Power services for PULP systems, Versal RPU access for low Power Services, agreement Protocol for Low-Power Services, and Versal Isolation Design- Functional Safety, in Sections 5, 6, 7, 8, 9, 10 respectively. Next, we describe how the LEDEL library is validated for low-power services in Section 11. Finally, in Section 12, we draw the conclusions.

| Copyright © FRACTAL Project Consortium | 11 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

|         | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

## 4 High-Level Picture

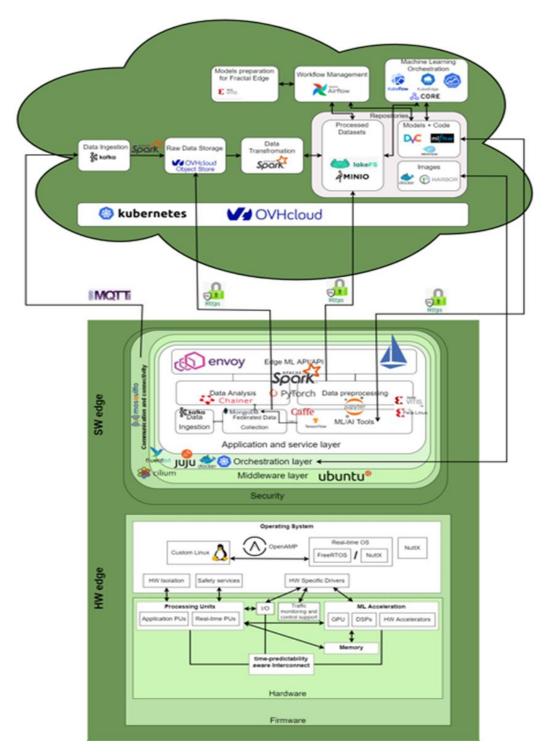

Figure 2 The big picture of the FRACTAL project

| Copyright © FRACTAL Project Consortium | 12 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |  |

|---------|-----------|----------------------------|--|--|

|         | Title     | FRACTAL Low-power services |  |  |

|         | Del. Code | D4.2                       |  |  |

The big picture of the project, illustrated in Figure 2, is a holistic representation of the FRACTAL solution which aims to illustrate the assembly of the components to build the FRACTAL node. It provides an answer to the use cases' requirements, which are the functional and non-functional needs captured by FRACTAL use cases at the beginning of the project. Starting from these requirements, a set of features could be established to give a technical notion to the requirements.

Beginning with the platforms' hardware and low-level software layers, one may interpret the picture from the bottom up (OS, services, drivers...). The various edge application software layers are integrated on top of them. Finally, this node communicates with its cloud counterpart that includes for instance learning and orchestration.

In the following subsections we report how each of the T4.1 components mentioned in Chapter 3 is integrated into the big picture.

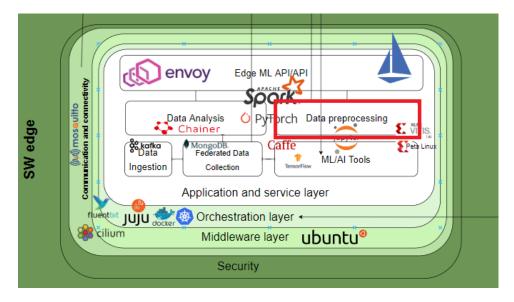

#### **4.1 Data Compression for low power services**

The Data Compression component has been developed at the software level thus, it could be regarded as a part of the software edge of the big picture. Specifically, it might be considered as a component of the data preprocessing block highlighted in Figure 3 and can be integrated into any component needing data compression/decompression functionalities.

Figure 3 The integration of Data Compression component in the big picture

| Copyright © FRACTAL Project Consortium | 13 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |  |

|---------|-----------|----------------------------|--|--|

|         | Title     | FRACTAL Low-power services |  |  |

|         | Del. Code | D4.2                       |  |  |

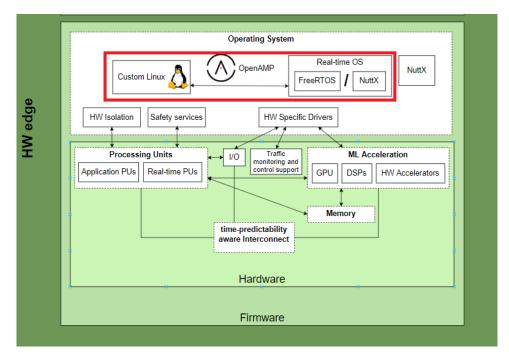

## **4.2 HATMA**

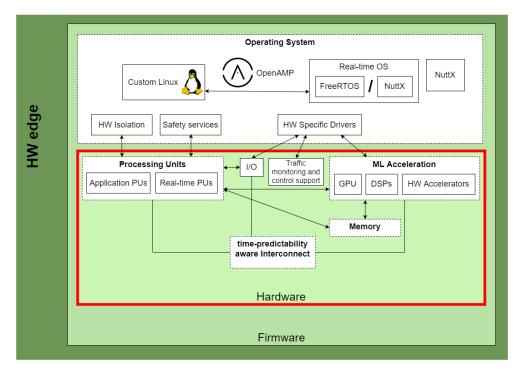

HATMA employs a time-predictable/aware interconnect to provide communication services between processing units, I/O, shared memory, and ML accelerators. Traffic monitoring and control are supported through time-triggered scheduling of system resources. HATMA integrates vertically with the operating system to deliver system services and horizontally to other FRACTAL nodes to deliver hierarchical services.

Figure 4 HATMA integration in the FRACTAL big picture

| Copyright © FRACTAL Project Consortium | 14 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |  |

|---------|-----------|----------------------------|--|--|

|         | Title     | FRACTAL Low-power services |  |  |

|         | Del. Code | D4.2                       |  |  |

#### **4.3 Low Power services for PULP systems**

The component aims at enhancing the low-power services of PULP systems. Finegrained power gating has been explored to minimize the power consumption powering off unused hardware units and allowing tuning the hardware configuration for specific application scenarios. Use cases built upon PULP-based end nodes will take advantage of the additional features to build low-power and efficient IoT applications, reaching higher battery life.

Figure 5 The integration of low power services for PULP systems in the big picture

| Copyright © FRACTAL Project Consortium | 15 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |  |

|---------|-----------|----------------------------|--|--|

|         | Title     | FRACTAL Low-power services |  |  |

|         | Del. Code | D4.2                       |  |  |

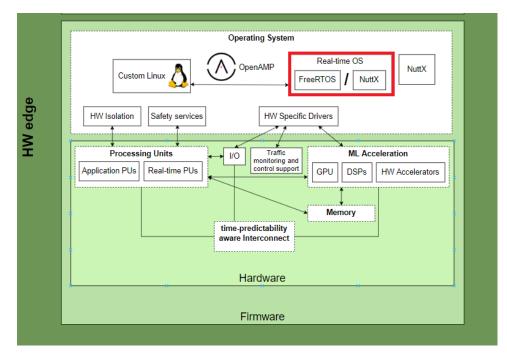

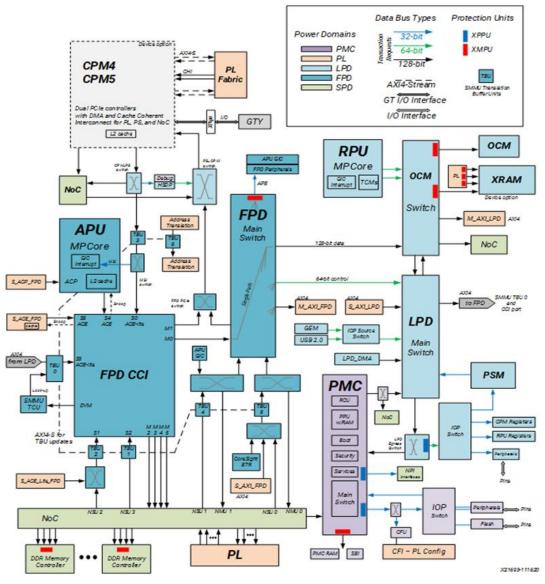

### 4.4 Versal RPU access for Power Services

This component provides means to access dynamic power and frequency scaling features on Versal in safety-oriented platform designs. Thus, FRACTAL node-level services and software applications from use-cases can query or control power state through this access layer. Low power features must utilize this safety access channel introduced by this component in order to adhere to isolation defined for a safety-centric design as in Section 4.6.

Figure 6 The integration of Versal RPU access for low power services in the big picture

| Copyright © FRACTAL Project Consortium | 16 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |  |

|---------|-----------|----------------------------|--|--|

|         | Title     | FRACTAL Low-power services |  |  |

|         | Del. Code | D4.2                       |  |  |

### **4.5 Agreement Protocol for Low-Power Services**

For the agreement protocol, we are using FreeRTOS as a component to perform tasks for synchronization of the peers. It integrates into the Hardware platform of the big picture as shown in Figure 7. The FreeRTOS tasks handle the whole synchronization protocol starting from the selection of master among a group of nodes, sending SYNC messages, and handling of cases when the peer connection is lost. The nodes are low powered microcontrollers (ESP-32).

Figure 7 The integration of agreement protocol in the big picture

| Copyright © FRACTAL Project Consortium | 17 of 80 |

|----------------------------------------|----------|

|                                        |          |

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |  |

|---------|-----------|----------------------------|--|--|

|         | Title     | FRACTAL Low-power services |  |  |

|         | Del. Code | D4.2                       |  |  |

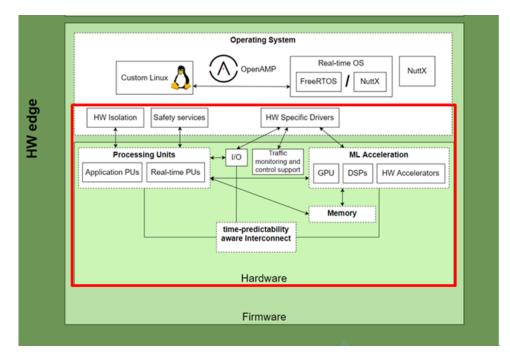

## 4.6 Versal Isolation Design- Functional Safety

To fulfil the requirements for a safety-focused Versal design the basic accessibility of the generic platform is restricted as a base for proper functional safety capabilities. This component defines a particular policy to support a safety channel that encapsulates the device and board infrastructure. The definition of the safety channel has been provided in Deliverable *D2.2 - 6.3.2.3 Versal Safety Channel Architecture* and encapsulates the power functionality with a specific RPU core. Resources within this safety channel are accessible from the application layer through this RPU power control software component as described in Section 4.4.

Figure 8 Location of the Versal isolation features in the big picture

| Copyright © FRACTAL Project Consortium | 18 of 80 |

|----------------------------------------|----------|

|                                        |          |

|         | Project   | FRACTAL                    |

|---------|-----------|----------------------------|

| FRACTAL | Title     | FRACTAL Low-power services |

|         | Del. Code | D4.2                       |

## 5 Data Compression for Low-Power Services - WP4T41-01 - ROT

### **5.1 LZW compression technique**

As it was stated in the deliverable D4.1, a variety of compression techniques could be used in energy-constrained systems in order to minimize the data exchanged among nodes and thus reduce the network energy consumption. These techniques could be classified based on some parameters such as application type, data quality, coding schemes, and data type. In addition, we have provided the state of the art of possible data compression algorithms and data aggregation techniques that could be used in such networks. Moreover, according to the Use Cases requirements, we have set out some specific features which should be taken into careful consideration in order to choose a suitable data compression technique. Satisfying these features, it was decided to choose the LZW algorithm. The LZW algorithm is a very common compression technique that is typically used in text file, TIFF, GIF and optionally in PDF. The main features of the algorithm:

- Lossless algorithm, no information loss during the processing;

- Excellent compression/decompression speed;

- Good compression ratio;

- Dictionary-based operating principle (the algorithm is an evolution of the first known dictionary algorithms, LZ77 and LZ78);

- Ability to compress streaming data without knowing the data before compression;

- Simple implementation, with a potential for very high throughput in hardware implementations;

LZW is the foremost technique for general purpose data compression due to its simplicity and versatility. It is the basis of many PC utilities that claim to double the capacity of your hard drive. LZW is mainly used in the compression of text and images in the most well-known existing formats. Although its diffusion is still rather limited compared to algorithms based on LZ77, it is widely used Unix file compression utility compress and is used in the GIF image format.

Its main advantage over other algorithms is that it uses a dictionary that is built up as it reads a file or stream of data.

The working principle of a dictionary algorithm consists in replacing a set of recurring symbols with abbreviated symbols in the output data. The idea relies on reoccurring patterns to save data space.

To give an example of an algorithm with a dictionary, we can imagine compressing an SMS by replacing the most used words with numbers. For example, using 16bit we could have 65535 words in our new compressed dictionary, more than enough to compose an SMS with a simple language. The saving of this imaginary algorithm in

| 1995200 A | Project   | FRACTAL                    |  |

|-----------|-----------|----------------------------|--|

| FRACTAL   | Title     | FRACTAL Low-power services |  |

|           | Del. Code | D4.2                       |  |

terms of data would be considerable; in fact, each word could occupy even only 2 symbols (in computer science each character of text occupies 8bit), with such a compression we could get to compose SMS with a much higher number of words. compared to a classic SMS.

As we often have to work with very varied and non-recursive data, finding a good algorithm for many cases is no small feat, but it is precisely what LZW guarantees.

The working of the LZW algorithm for compression is as follows:

STRING = INPUT CHARACTER WHILE there are characters in DO input CHARACTER = read unput IF STRING + CHARACTER is present in the then dictionary STRING = STRING + CHARACTER ELSE write the dictionary symbol of STRING add STRING + CHARACTER in the dictionary STRING = CHARACTER END of IF END of WHILE write the dictionary symbol of STRING

Figure 9 LZW compression algorithm

To better understand the process, let's take for example a word to be compressed consisting of 11 characters: ABCABEFGHIL.

The dictionary is initialized with 256 symbols, an array of strings of single character, which also contain each of the single characters of the word mentioned above: A B C E F G H I L.

After the first reading, the input buffer will consist of: A.

In the second step, the algorithm reads B, and the buffer becomes: AB.

AB is a symbol not present in the dictionary, at this point the algorithm inserts the new symbol AB in the first position available in the dictionary, i.e., position 256 which will therefore contain the new symbol.

Once this symbol has been added, the algorithm will produce an output corresponding to the position of the last symbol found, i.e., the value of the position associated with character A, precisely: 65.

| Copyright © FRACTAL Project Consortium | 20 of 80 |

|----------------------------------------|----------|

|                                        |          |

| (1995)<br>(1995) | Project   | FRACTAL                    |  |

|------------------|-----------|----------------------------|--|

| FRACTAL          | Title     | FRACTAL Low-power services |  |

|                  | Del. Code | D4.2                       |  |

The algorithm proceeds by discarding the symbol sent out from the buffer and appending the new byte to be read at the last read, the buffer thus becomes BC. The new symbol BC is not present in the dictionary thus the algorithm inserts the new symbol BC in position 257, and always returns as output the value of the position of the last symbol which is in this stage 66 associated with the symbol B.

The process continues and the buffer becomes CA which is not present in the dictionary too, thus the algorithm outputs the position of the symbol C that is: 67, and inserts the new symbol CA in position 258.

In the next step the buffer becomes AB, AB is a symbol in the dictionary, the algorithm does not produce any output and continues with the reading (the compression begins).

The buffer then becomes: ABE which is not present in the dictionary. Therefore, the output is 256 (the value of the symbol AB), and the new symbol inserted in the dictionary is: ABE with the value 259 and the buffer becomes EF.

The algorithm proceeds in this way until the incoming data ends.

Decompression proceeds in a very similar way to compression, so the algorithm of decompression can be expressed as in Figure 10:

Read OLD CODE Write OLD\_CODE CHARACTER = OLD\_CODE WHILE there are characters in DO input Read NEW CODE IF NEW\_CODE is not in the THEN dictionary STRING = string in the dictionary with code OLD\_CODE STRING = STRING + CHARACTER ELSE. STRING = string in the dictionary with NEW\_CODE code END IF Write STRING CHARACTER = first character in STRING add OLD\_CODE + CHARACTER in the dictionary OLD\_CODE = NEW\_CODE END WHILE

Figure 10 LZW decompression algorithm

| 2452243 | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

Although the LZW algorithm is quite simple to understand from logical point of view, its implementation brings up considerable technical difficulties from practical point of view:

- 1) The use of memory must be optimized within the code where the system must store a very large dictionary in a small space.

- 2) The search for symbols in the dictionary must be optimized to reduce data processing time.

- 3) Symbols must be written in a format with variable bit-size depending on the size of the dictionary during the compression phase to maximize the benefits of the algorithm.

- 4) Since the size of memory is limited, it is necessary to limit the size of the dictionary.

- 5) The dictionary must be reset when it becomes full or the compression ratio becomes inconvenient since during compression with this method the compression ratio tends to degrade very easily depending on the portion of data to be compressed.

With an eye toward achieving the main objective of the T4.1 to ensure the energy efficiency of the FRACTAL system, we proposed some possible solutions of the aforementioned challenges such as:

- 1) To limit the space occupied by the dictionary, you can keep in memory only a list of pairs of variables for each symbol of the dictionary. In other words, a prefix/last character pair, while the code in the dictionary will be nothing more than the index of the array used. In particular, it can be seen that each new symbol to be inserted in the dictionary is nothing more than an old symbol in the dictionary with one last extra character. It is, therefore, sufficient to memorize the value of the old symbol and the character that forms the new symbol instead of memorizing the whole new symbol which could be as long as the dictionary itself. For instance, by applying this technique on the first memorization step of the previous example, the insertion of the symbol AB in the dictionary becomes prefix 65-character B, array index 256.

- 2) With the aim of solving the problems of the search times of the symbols in the dictionary, a Hash algorithm is used in many implementations of LZW. Although this algorithm is more efficient than other data structures and it provides constant time for searching, it has some disadvantages. Specifically, using the Hash algorithm can have a considerable cost. It demands a necessary increase in the memory to be dedicated to saving the dictionary. Therefore, a large portion of the memory will be wasted to the detriment of the maximum compression capabilities.

An optimal solution has been analyzed which consisted in making the most of the hypothesized structure to store the dictionary. In particular, we considered that each prefix-character element of our structure is used to form other symbols of the prefix/character + second character type, and the maximum number of derived symbols will never be higher than 255 due to

|         | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

the operating principles of the algorithm. Then, we can add an array of 255 pointers for each prefix-character pair which point to the pairs derived from the source ones. The index of these pointers will be used with the second character. Despite the significant improvement this solution will lead to, where the cost of research with this structure would always be equal to 1, it involves excessive use of memory. One way to solve this drawback is to reduce the pointer arrays in order to create linked lists. Faster processing times are going to be required in UC6, where the analysis reported here is going to be implemented and integrated.

- 3) With the purpose of maximizing the effectiveness of this compression algorithm, the output values should be stored using only the needed space. This means that, for example, when a symbol with a position 256 is added to the dictionary which has a maximum size of 16 bits, the written value must occupy only 9 bits of the memory rather than 16 bits, as long as it does not need more bits for storage. In addition, the bit size has to grow dynamically according to the momentary size of the dictionary. This one will be solved and developed in another European project.

- 4) In order to limit the size of the memory, we defined the size of the dictionary. The best method used in this case is to give a limit to the dictionary based on a bit-size of the code-word. By doing so, there will be no wasted information in the compressed output. This means that if, for example, we use code-word of 14 bits, the maximum number of symbols in the dictionary will be

$2^{14} - 1 = 16383$  symbols

- 5) Since the compression ratio using the LZW algorithm tends to decline easily depending on the percentage of data to be compressed, the dictionary must be reset to prevent compression from degrading once the dictionary is full. In order to do so, we propose two methods which might be implemented in the next period. We are going to report this improvement on the related UC deliverable. These methods are:

- a) The first one is based on resetting the dictionary to return to the initial situation in which we have, for example, 255 symbols. In addition, one way to indicate to the decompression process that the dictionary starting from the special symbol has been reset is to reverse that symbol in the dictionary.

- b) The second technique is more refined. It focuses on the continuous analysis of the compression rate and resetting it every time the dictionary degrades.

In the following subsections, we report the implementation of LZW data compression, perform a set of practices and processes in order to validate our component, and determine if our component meets the project KPI metrics. Additionally, we address the use case which utilizes our component and how it is integrated into that use case.

| 2551243 | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

## 5.2 Design and implementation

The data compression component was designed to be split into two subcomponents: *Compression* and *Decompression* which both have a single entry-point for their respective action to be performed on the file taken as input.

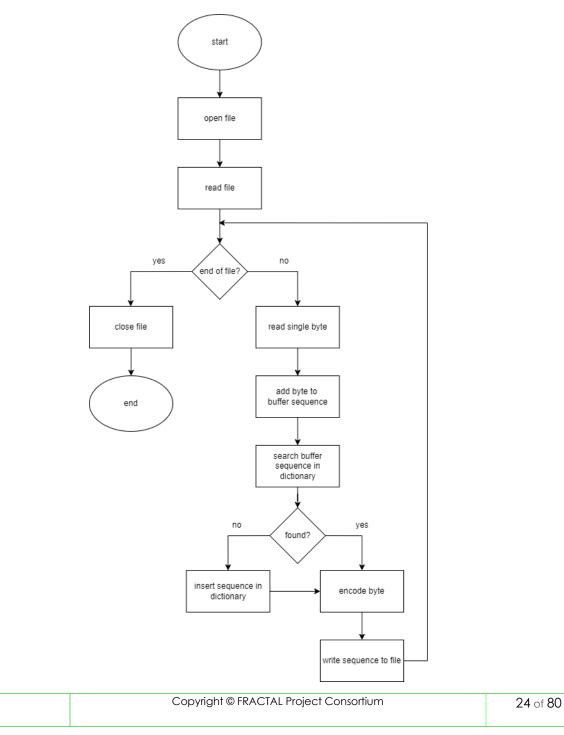

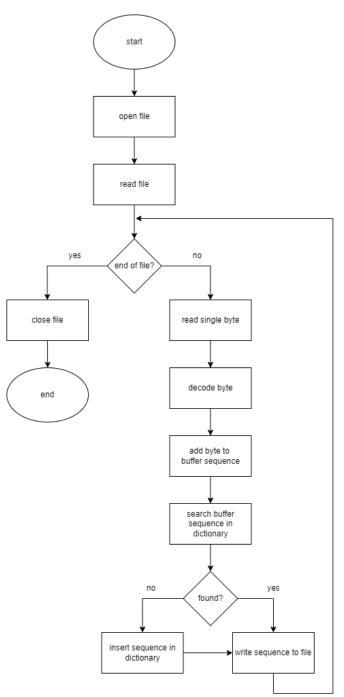

The following flowchart, Figure 11, explains the data flow of the Compression subcomponent library which takes as input path, name, and extension of the file to be compressed. It will read the original file and perform LZW compression to give as output a file on the same path, with the same name, and extension ".lzw".

| 255222  | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

Figure 11 The flow chart of the compression process

The flowchart in Figure 12 explains the data flow of the Decompression subcomponent library, which takes the same input as the Compression subcomponent (the file extension must be the same as the output file, since the input file is supposed to always be a previously compressed file, hence with the extension ".lzw".)

Figure 12 The flow chart of the decompression process

| Copyright © FRACTAL Project Consortium | 25 of 80 |

|----------------------------------------|----------|

|----------------------------------------|----------|

| 1995200 A | Project   | FRACTAL                    |  |

|-----------|-----------|----------------------------|--|

| FRACTAL   | Title     | FRACTAL Low-power services |  |

|           | Del. Code | D4.2                       |  |

The component was implemented as a software library, developed in C++, as a wrapper and extension of an open-source LZW C++ implementation. [9]

## 5.3 Testing and evaluation

The Data Compression component can be evaluated in several ways. Considering the different types of parameters, it is possible to define a series of tests that measure or calculate these parameters, through which it is, therefore, possible to provide evidence of the effectiveness of the component.

**Data compression ratio**, also known as **compression power**, is a measurement of the relative reduction in the size of data representation produced by a data compression algorithm. It is typically expressed as the division of uncompressed size by compressed size.

$$CR = \frac{US}{CS}$$

where CR is the *Compression Ratio*, US the *Uncompressed Size* of input file and CS the *Compressed Size* of output file. This formulation applies equally for compression, where the uncompressed size is that of the original; and for decompression, where the uncompressed size is that of the reproduction.

Another measurement of size reduction is **Space Saving**, which is defined as the reduction in size relative to the uncompressed size:

$$SS = 1 - \frac{CS}{US}$$

where SS is the *Space Saving*, CS is the *Compressed Size* the of output file, and US is the *Uncompressed Size* of the input file. This measurement provides a percentage value of the space saved with the compression process.

The third parameter to evaluate our component is the **time** for the compression and decompression processes, which is an important indicator of the efficiency of the algorithm.

The Lab tests were conducted on a Windows 10 computer with both compression and decompression algorithms compiled as a library.

During the lab tests, we focused on the **saved space** and the **time** needed for both compression and decompression.

Due to the fact that Data Compression component is going to be integrated in Use Case 6, tests have been conducted using sample files provided by the use case. This set of sample files is composed of images in JPEG format and audio in WAV format, and the tests have been performed using 14 different audio files. For further details about integration refer to section 5.3.1.

| Copyright © FRACTAL Project Consortium | 26 of 80 |

|----------------------------------------|----------|

|                                        |          |

| 2992243 | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

All the files that were used during the tests were successfully compressed apart from 3 cases. In the first one, the file size was the same as the original, and in the other two the size was greater than the original. However, it was expected that some files could not be compressed by one compression algorithm because no lossless compression technique can efficiently compress all types of data/messages. [10]

Given the limits of lossless data compression algorithms, we have reported the results of the successful tests performed to estimate the value of *Space Saving* in Table 2. The average compression and decompression times was, on the other hand, estimated among all the results of the tests.

As we notice from table below, the algorithm meets the KPIs identified during the requirements identification phase.

| KPI description                | Means of assurance | Expected | Measured/<br>Achieved |

|--------------------------------|--------------------|----------|-----------------------|

| ACCURACY<br>Saved space        | Lab test           | > 10%    | 12%                   |

| RESPONSE TIME<br>Compression   | Lab test           | < 3s     | 2.3 s                 |

| RESPONSE TIME<br>Decompression | Lab test           | < 3s     | 2.6 s                 |

| Table 2 KP | I and | metric | of | component | WP4T41-01 |

|------------|-------|--------|----|-----------|-----------|

|            | L and | meene  | ~  | component |           |

The next steps will be to perform improvement to meet the specific requirements of UC6 (Intelligent Totem) and for integration and field tests.

#### 5.3.1 Integration into UC6

The Data Compression component is going to be integrated into UC6, which is expected to use to reduce the amount of the data transferred between nodes. In particular, the Data Compression is used when the Load Balancer component is triggered, meaning the current node is overloaded and needs to distribute workloads.

As we mentioned, the component could be utilized to compress/decompress various media types. Referring to *D8.1* - *Specification of Industrial validation Use Cases*, the first proposed way of integration was to use our component in the compression/decompression of the images taken by the node camera. However, the images provided by the node have JPEG format, which is not suitable for the LZW algorithm. Furthermore, JPEG is a method of compression for digital images, so using the LZW compression on a .jpeg image does not produce an admissible result. These images could be sent to other nodes while all the UC6 requirements are fulfilled among which is the time constraint.

| Copyright © FRACTAL Project Consortium | 27 of 80 |

|----------------------------------------|----------|

|                                        |          |

| 255-27-23 | Project   | FRACTAL                    |  |

|-----------|-----------|----------------------------|--|

| FRACTAL   | Title     | FRACTAL Low-power services |  |

|           | Del. Code | D4.2                       |  |

However, using it with the type of image captured by the node's camera in UC6, will do a reverse job and expand the output file. Therefore, we decided to use the compression technique to compress the audio files captured by the node's microphone. In fact, the tests reported in section 5.3 have been conducted using sample audio files.

| Copyright © FRACTAL Project Consortium | 28 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Title     | FRACTAL Low-power services |  |

|---------|-----------|----------------------------|--|

|         | Del. Code | D4.2                       |  |

## 6 Hierarchical Adaptive Time-triggered Multi-core Architecture (HATMA) -WP4T41-02 - SIEG

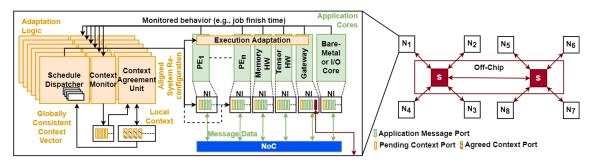

The Hierarchical Adaptive Time-triggered Multi-core Architecture (HATMA), as introduced in D4.1, delivers services through adaptation on two levels, the system and node levels. The system-level encompasses nodes interconnected through a time-triggered off-chip communication network. Access to the network is provided via a gateway, which encrypts and decodes messages before injecting them into the network to their intended destination. On the other hand, the node level encompasses processing elements and a time-triggered network-on-chip to facilitate message exchanges within the node. Each processing element within a node is interfaced with a network interface which injects messages from the processing element into the respective network.

As illustrated in Figure 13, each processing element includes computational cores for application services, an adaptation logic, and a network interface for accessing the adaptive communication network and the network-on-chip. In the case of the gateway core, the network interface is used to access the off-chip communication network.

Figure 13 Hierarchical Adaptive Time-triggered Multi-core Architecture (HATMA)

A consistent state of all resources facilitates hierarchical adaptation in HATMA at periodic points in a scheduled period. The time-triggered schedules maintain such consistency. Adaptation is then achieved at the different hierarchies by an aligned switching of schedules in response to context events such as dynamic slack for low power and energy management services.

## **6.1 HATMA Subcomponents**

The adaptation logic of HATMA manages and coordinates adaptation services in a distributed manner and comprises the context monitor, context agreement unit and schedule dispatcher. Therefore, hierarchical adaptation is synchronized across all adaptation logics at the respective hierarchy. The establishment of a consistent system state is taken in a distributed manner by all context agreement units. The

| Copyright © FRACTAL Project Consortium | <b>29</b> of <b>80</b> |

|----------------------------------------|------------------------|

|                                        |                        |

| 2992243 | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

adaptation logic establishes a global view of the system state. A global system state is realized through observation, reporting, broadcast, distribution and agreement of local contexts. Therefore, the selection and dispatch of the following schedules for hierarchical adaptation are possible based on the agreed contexts as described in Figure 14:

Figure 14 HATMA Adaptation Logic Process

**Context monitor (CM)**: The CM observes the state of its local system resource and generates local context information. Such local context can be the status of an application being executed on a core. The local resource is periodically observed for each scenario based on the precomputed adaptation schedule. The precomputed adaptation schedule for the periodic sampling of the local resource is synchronized to the system schedule to enable a potential schedule change without detriment to the system.

**Context Agreement Unit (CAU):** Through the Hierarchical Interactive Consistency Protocol (HICP), the CAUs establish a globally consistent context vector (system state) by collecting and agreeing on the local contexts reported by all CMs at the respective hierarchy.

- a. All CAUs initiate a synchronized context distribution phase based on a precomputed adaptation schedule. Through the HICP, the local context is distributed in a double-ring topology through the adaptation communication network. Local context is sent to and collected from the next neighbors in the network and concatenated to produce a global context vector.

- b. At the end of the distribution phase, all resources possess identical system information. At this point, HICP converges, and the CAUs agree on the system state. The agreed context vector is the globally consistent context vector representing the system status at all resources. The schedule dispatcher uses the globally consistent context vector to determine the next schedule and perform an aligned switching of schedules at runtime.

**Schedule Dispatcher**: The precomputed multi-schedule graph is stored in this unit. The next dispatched schedule is chosen based on the globally consistent context vector from the CAU mapped to the edges in the multi-schedule graph. Based on the system state, adaptation is achieved by choosing the next schedule and dispatching it for an aligned reconfiguration of the respective hierarchy of the system. At the start

| Copyright © FRACTAL Project Consortium | 30 of 80 |

|----------------------------------------|----------|

|                                        |          |

|         | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

| FRACTAL | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

of the adaptation window, the CMs are triggered, and an instance of the HICP is initiated. At the end of the window, the schedule dispatcher performs an aligned schedule change in adaptation to the agreed observed contexts.

#### 6.1.1 Hierarchical Interactive Consistency Protocol (HICP)

The context event to be monitored influences the timing of instances of the HICP at the various hierarchies. Context events are differentiated based on their urgency. The urgency of a context event indicates a period when adaptation to the event can yield a benefit before it loses its value for adaptation. For example, urgent slack events require fast switching at the core and node levels to trigger low power and energy management services. On the other hand, adaptation at the system level is much slower given the number of resources and the communication cost of the offchip communication.

Furthermore, adaptation generally introduces overhead. Thus, the system level's adaptation frequency has a coarser granularity to balance the increased overhead. Slowly changing events such as the available power in battery-operated devices or events critical to overall system reliability are prioritized at the system level given the adaptation window and the constraints of adaptation overhead.

### 6.2 Design and implementation

HATMA is instantiated in hardware using the Xilinx Vivado design suite and Vitis toolchain for synthetic slack scenarios to validate the HATMA low power service. A multi-core architecture consisting of a Zynq processing system and 3 Microblaze cores, the adaptation logic and the Adaptive Time-Triggered Network-on-Chip (ATTNoC) described in deliverable D4.1 was instantiated on a Xilinx Zynq UltraScale+ MPSoC ZCU102 FPGA board.

The adaptation logic for HATMA is key to the timely and consistent reporting, agreement and adaptation of HATMA to context events. During each adaptation period, local resources are observed, and local context is reported. Then, through the HICP, observed local contexts are broadcast to neighboring resources and an agreed system state at the respective hierarchy is established. The agreed system state allows for an aligned hierarchical adaptation to the observed events. Therefore, adaptation at the node level is consistent with the global system state.

#### 6.2.1 Context Monitor (CM)

The CM is triggered to monitor and report the status of its local resource, for example, dynamic slack of the jobs of an application service running on a core. The CM can be realized in hardware and software and is designed to poll and report local context information.

Synchronous events are predictable, and CMs can be scheduled to observe such events. On the other hand, asynchronous events are random and are therefore observed through periodic monitoring of system resources. In either case, there is a polling delay between the occurrence of a context and its reporting. Therefore, a

| 1995200 A | Project   | FRACTAL                    |  |

|-----------|-----------|----------------------------|--|

| FRACTAL   | Title     | FRACTAL Low-power services |  |

|           | Del. Code | D4.2                       |  |

time-triggered adaptation of system resources is scheduled periodically, where the granularity is a trade-off between a reduced polling delay and adaptation overhead.

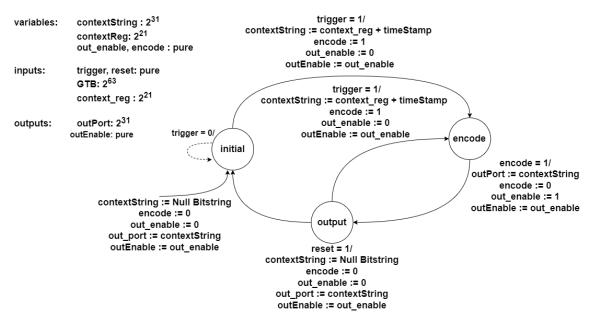

A CM implemented in hardware using a finite state machine is described in Figure 15. The time-triggered machine reacts to an external trigger and a reset. It starts in the *initial* state where no context is observed, and its reported context is initialized to null. When triggered, it transitions to the *encode* state. It monitors and records the local resource state based on observable information (dynamic slack) and the context time (timestamp). When the observed local context is encoded into a 32-bit bitstring, it transitions to the *output* state when the encoded context bitstring is driven at the output. At the output state, the machine transitions back to the *initial* state when reset or to the *encode* state when the CM is triggered. The machine remains in the *output* state when no trigger or reset is present.

Figure 15 Context Monitor Implemented in Hardware using a Finite State Machine

In each case, triggers are generated based on the precomputed adaptation schedule. Such operation of the machine allows for a periodic observation and reporting of context events in multiple instances. The outputs produced by this machine are the encoded local context and *outEnable* to indicate the availability of the observed context.

#### 6.2.2 Context Agreement Unit (CAU)

The CAU manages instances of the HICP when reported local contexts are broadcast to neighbors in a dedicated double-ring half-duplex network topology. Each instance of the HICP across multiple CAUs is synchronized to realize an aligned convergence of the HICP. On the convergence of HICP, each CAU possesses an identical global view of the system state, which is the basis for hierarchical adaptation.

The CAUs are triggered periodically within adaptation windows in the system schedule. For example, in one instance of the HICP, the local context provided by

| Copyright © FRACTAL Project Consortium | 32 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

|         | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

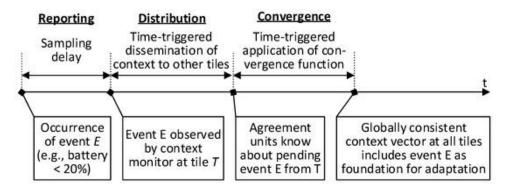

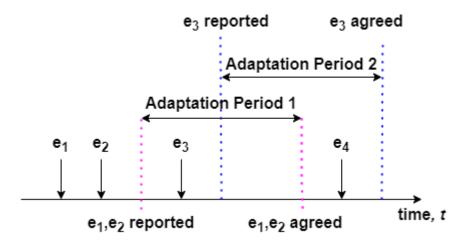

CMs is frozen in time and agreed upon by all CAUs. The following instance of the HICP is used to agree on the next set of reported events, as illustrated in Figure 16. Each received local context is saved to the local register and relayed to the next neighbour until the local context gets to the initial broadcaster when the instance of the HICP is converged.

Figure 16 Periodic Adaptation to Context Events

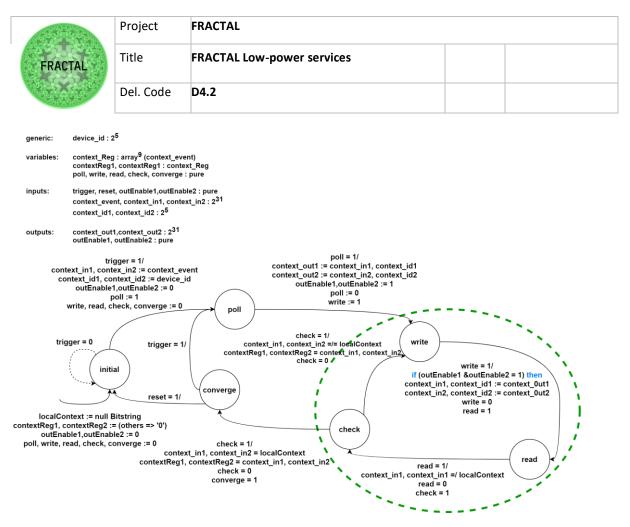

A CAU implemented in hardware using a finite state machine is described in Figure 17. In the figure, the machine reacts to a trigger and a reset. It starts in the *initial* state where its local registers are initialized and its output disabled. Each received context bitstring is assigned a unique slot in the local registers based on its CAU ID. When a trigger is present, it transitions to the *poll* state, where context events reported by CMs are saved in two registers and held as input context. In this state, the CAU's local ID is also the CAU ID of origin for the input context.

| Copyright © FRACTAL Project Consortium | 33 of 80 |

|----------------------------------------|----------|

|                                        |          |

Figure 17 Context Agreement Unit Implemented in Hardware using a Finite State Machine

When the context event is collected and saved, the machine transitions to the write state, where the input contexts are written to the two output ports. The CAU ID of origin and an indication of the context availability are also driven as outputs. At the end of the writing process, the machine transitions to the read state, where inputs from neighbors in the double-ring are read synchronously from the input ports. These contexts from neighbors are saved to the local register and held as input contexts. The CAU ID of the context origin of the received contexts is also stored in this state. The machine then transitions to the *check* state, where the received CAU IDs are checked against the local CAU ID. If any of the received CAU IDs match the local CAU ID, the machine transitions to the *converge* state and terminates the HICP. The machine returns to the *write* state and drives the respective inputs to the output ports if the CAU IDs do not match the local CAU ID. The machine maintains the writeread-check loop synchronously across all CAUs in the network until it transitions to the converge state, as shown in Figure 17 (Green circle). When in the converge state, the machine transitions back to the *initial* state when reset input is present or to the *poll* state when a trigger is present. The machine remains in the *converge* state when no trigger or reset is present.

Triggers for the CAUs are based on the current schedule and are synchronized across all CAUs. The aligned and periodic triggers for the CMs and CAUs allow for parallel instances or periods of adaptation based on Figure 16. For example, an instance of adaptation can be in the distribution phase, and the next instance of adaptation can begin with the reporting phase. In each instance, the outputs produced by the CAUs are the agreed context bitstrings and the trigger signal for schedule change.

| Copyright © FRACTAL Project Consortium | 34 of 80 |

|----------------------------------------|----------|

|                                        |          |

| FRACTAL | Project   | FRACTAL                    |  |

|---------|-----------|----------------------------|--|

|         | Title     | FRACTAL Low-power services |  |

|         | Del. Code | D4.2                       |  |

## 6.3 Testing and evaluation

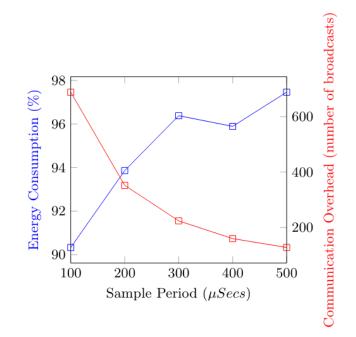

The timely adaptation to context events at runtime is desired to increase the efficiency of HATMA's adaptation. In addition, adaptation through HATMA should also result in energy savings for low-power applications. Therefore, the evaluation of HATMA's adaptation for low-power is based on four key metrics: polling delay, time to convergence, overhead and energy saving.

**Polling Delay:** HATMA's adaptation is time-triggered and executed based on a precomputed adaptation schedule. This periodic execution introduces a delay between the occurrence of a context event and when the adaptation logic reports such context event, referred to as the polling delay  $\delta$ . Runtime events are generally asynchronous due to the unpredictability of their occurrence. To minimize the polling delay, we introduce a timing granularity  $\tau$  of adaptation where the system is sampled periodically between 100 and 500µs. This range of granularity ensures that all scheduled tasks are sampled at least once for the occurrence of a slack event relevant for adaptation for energy saving. This range also ensures that sufficient time is available to adapt the system schedule. We also simulate a schedule of 20 and 100 tasks with hard deadlines and worst-case execution times (WCET) in the range of 700 - 1000µs on the architecture.

On average, 70% of application tasks are completed in 50% of their WCET [1] where the maximum polling delay is such that:

$\delta_{\max} = \tau$ ,

where the timing granularity of adaptation is applied globally to the system schedule. A 100µs timing granularity represents a frequent sampling of the system every 100µs. The more frequent the system is sampled, the lower the polling delay and the faster HATMA adapts to observed events. For example, HATMA exploits the early completion of tasks (slack events) to apply Dynamic Voltage and Frequency Scaling (DVFS) and Power/Clock gating techniques to save energy. Therefore, the system is frequently sampled for highly volatile events such as slack, in which energy saving decreases as the polling delay increases.