# Deliverable

## D3.6 Software node and services architecture

| Deliverable Id:                  | D3.6                                                                                                                                                                                                      |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deliverable Name:                | Software node and services                                                                                                                                                                                |

|                                  | architecture                                                                                                                                                                                              |

| Status:                          | Approved                                                                                                                                                                                                  |

| Dissemination Level:             | Public                                                                                                                                                                                                    |

| Due date of deliverable:         | 30.9.2022                                                                                                                                                                                                 |

| Actual submission date:          | 20.10.2022                                                                                                                                                                                                |

| Work Package:                    | WP3                                                                                                                                                                                                       |

| Organization name of lead        | Offcode Oy                                                                                                                                                                                                |

| contractor for this deliverable: |                                                                                                                                                                                                           |

| Author(s):                       | Antti Takaluoma                                                                                                                                                                                           |

| Partner(s) contributing:         | Alexander Flick, PCL2<br>Jérôme Quévremont, Thales<br>Kévin Eyssartier, Thales<br>Jaume Abella, BSC<br>Ramon Canal, BSC<br>Edurne Palacio, Ikerlan<br>Lauri Loven, UOULU<br>Leticia Pascual, Solver (SML) |

Abstract: This deliverable (D3.6) is the third of a series of deliverables that describe the software work for the FRACTAL project software nodes. This is the third of three deliverables on software node, and it will be updated throughout the project with D3.2, and D3.4.

This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 877056

Co-funded by the Horizon 2020 Programme of the European Union under grant agreement No 877056.

Copyright © FRACTAL Project Consortium

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

| His  | story. |        |                                                                 | 4       |

|------|--------|--------|-----------------------------------------------------------------|---------|

| 1    | Sun    | nmar   | ry                                                              | 5       |

| Lis  | t of W | /P3 c  | components                                                      | 7       |

| 1    | L.1    | Intr   | oduction                                                        | 8       |

| 1    | 1.2    | Арр    | lication owner view                                             | 8       |

|      | 1.2.   | 1      | Support for business logic                                      | 8       |

|      | 1.2.   | 2      | Support for development and testing                             | 9       |

|      | 1.2.   | 3      | Support for commissioning, deployment and provisioning          | 9       |

| 1    | 1.3    | End    | -user view                                                      | 9       |

| 2    | WP3    | 3 and  | d related WPs                                                   | 10      |

| 2    | 2.1    | WP3    | 3 and WP4                                                       | 10      |

|      | 2.1.   | 1      | Supporting FRACTAL developments on safety                       | 10      |

|      | 2.1.   | 2      | Supporting FRACTAL developments on security                     | 10      |

|      | 2.1.   | 3      | Supporting FRACTAL developments on low power                    | 10      |

| 2    | 2.2    | WP3    | 3 and WP5                                                       | 11      |

|      | 2.2.   | 1      | Supporting FRACTAL developments on AI                           | 11      |

|      | 2.2.   | 2      | LEDEL to develop and execute AI-based models in a FRACTAL node  | 17      |

|      | 2.2.   | 3      | Drivers for the software diverse redundancy library (WP3T34-02) | 25      |

|      | 2.2.   | 4      | Driver for the Edge-Oriented Monitoring Unit (WP3T34-01)        | 27      |

|      | 2.2.   | 5      | Driver for SIEFRACC accelerator (WP3T35-01)                     | 30      |

| 2    | 2.3    | WP3    | 3 and WP5                                                       | 31      |

|      | 2.3.   | 1      | Supporting FRACTAL developments on cognitive awareness          | 31      |

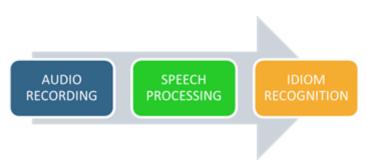

|      | 2.3.   | 2      | Idiom Recognition                                               | 34      |

| ź    | 2.4    | WP3    | 3 and WP6                                                       | 36      |

|      | 2.4.   | 1      | Supporting FRACTAL framework consistency                        | 36      |

|      | 2.4.   | 2      | Supporting FRACTAL application consistency                      | 36      |

| 3    | Role   | e of c | different platforms in FRACTAL Use Cases                        | 37      |

|      | 3.1    | Cust   | tomizable node (RISC-V based PULP)                              | 38      |

|      | 3.1.   | 1      | Pulp onboard resources                                          | 40      |

|      | 3.1.   | 2      | Safety considerations on Nuttx Pulp – WP4                       | 41      |

|      | 3.1.   | 3      | AI processing on Nuttx Pulp WP5                                 | 41      |

|      | 3.1.   | 4      | Application orchestration on Nuttx Pulp – WP6                   | 42      |

|      | 3.2    | Vers   | sal node                                                        | 43      |

| V0.1 | 6      |        | Copyright © FRACTAL Project Consortium                          | 2 of 61 |

|      |        |        |                                                                 |         |

|         | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

| A TANK  | Del. Code | D3.6                                                                                                              |

|          | 3.2.1     | Versal onboard resources46                  |

|----------|-----------|---------------------------------------------|

|          | 3.2.2     | Safety considerations on Versal – WP446     |

|          | 3.2.3     | AI processing on Versal WP547               |

|          | 3.2.4     | Application orchestration on Versal – WP647 |

| 3        | .3 Oth    | er nodes                                    |

|          | 3.3.1     | NOEL-V                                      |

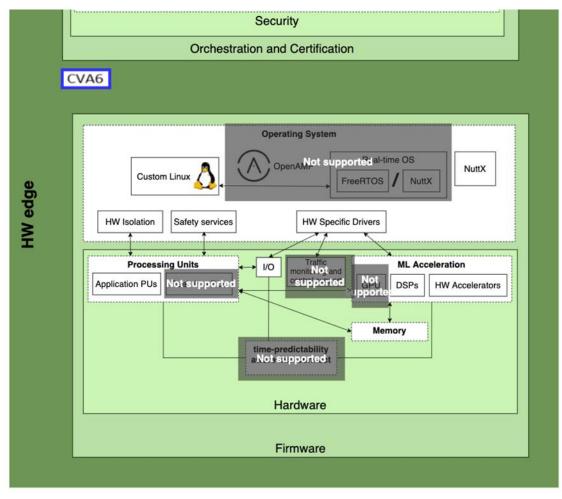

|          | 3.3.2     | ARIANE/CVA6                                 |

|          | 3.3.3     | Yet additional platforms 50                 |

| 4        | Interact  | ion of UCs with FRACTAL nodes51             |

| 5        | Conclus   | ions 52                                     |

| 6        | Next ste  | eps53                                       |

| 6        | .1 Ris    | ks and Mitigation plans53                   |

| 7        | Deviatio  | ons from workplan55                         |

| 8        | Bibliogr  | aphy56                                      |

| 9        | Referen   | ces 57                                      |

| 10       | List of f | igures                                      |

| 11       | List of t | ables59                                     |

| 12       | List of A | Abbreviations                               |

| <u> </u> |           |                                             |

### Contents

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

# History

| Version | Date       | Modification reason                                                                                                                                                                                          | Modified by            |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 0.17    | 11.10.2022 | Fixed names and added references to figures. Fixed grammar mistakes                                                                                                                                          | Leticia Pascual (SML)  |

| 0.16    | 10.10.2022 | Formatting (removed textboxes, added captions to<br>figures / tables, added bibliography, fixed header<br>table, fixed footer, removed white spaces before<br>paragraph breaks) TODO: fix references in text | Levente Tamas (OFFC)   |

| 0.15    | 3.10.2022  | Document format refactored                                                                                                                                                                                   | Levente Tamas (OFFC)   |

| 0.14    | 23.7.2022  | BSC contributions included                                                                                                                                                                                   | Jaume Abella (BSC)     |

| 0.13    | 21.6.2022  | Copied to be a base for D3.6                                                                                                                                                                                 | Antti Takaluoma        |

| 0.12    | 30.3.2022  | Final formatting changes                                                                                                                                                                                     | Antti Takaluoma        |

| 0.11    | 30.3.2022  | Updates based on internal review and various optimization to document.                                                                                                                                       | Antti Takaluoma        |

| 0.10    | 11.3.2022  | Moving chapters                                                                                                                                                                                              | Antti Takaluoma        |

| 0.9     | 1.3.2022   | Ready for review by Matti Vakkuri and Igor Bisio                                                                                                                                                             | Wp3 meeting            |

| 0.8     | 28.2.2022  | Proposal to be approved                                                                                                                                                                                      | Antti Takaluoma        |

| 0.7     | 28.2.2022  | Reviews and updates                                                                                                                                                                                          | Alexander Flick        |

| 0.6     | 25.2.2022  | Added "big pictures"                                                                                                                                                                                         | Jaume Abella (BSC)     |

| 0.5     | 23.2.2022  | Reviews and updates                                                                                                                                                                                          | Jérôme Quevremont      |

| 0.4     | 17.2.2022  | Proposal, prepared to project internal review                                                                                                                                                                | Antti Takaluoma (OFFC) |

| 0.3     | 31.12.2021 | Draft, filled D3.2 data to new structure, yellow text to be revisited                                                                                                                                        | Antti Takaluoma (OFFC) |

| 0.2     | 30.12.2021 | Draft, adding content                                                                                                                                                                                        | Antti Takaluoma (OFFC) |

| 0.1     | 29.12.2021 | Draft, basic structure revisited                                                                                                                                                                             | Antti Takaluoma (OFFC) |

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

### **1** Summary

The main objective of the FRACTAL project is to "create a cognitive edge node enabling a fractal Edge that can be qualified to work under different safety-related domains". Furthermore, it is stated in the DoA that "This computing node will be the basic building block of intelligent, scalable and non-ergodic IoT". As such the hardware node is a central part of the FRACTAL project around which 28 partners collaborate, investigate and industrial partners develop their use cases.

This deliverable (D3.6) is the third of a series of deliverables that describe the software work for the FRACTAL project hardware nodes. These documents will be delivered throughout the project with D3.2 (M12), D3.4 (M18), and D3.6 (M20). These three deliverables are also paired with the "hardware node and services" deliverables D3.1, D3.3 and D3.5.

The FRACTAL project brings together many partners (28) both from industry and academia, working on varied and challenging topics as well as eight industrial use cases. It was already a challenging task to provide a set of solutions for the hardware node in this context and combined with restrictions around COVID and worldwide supply disruptions for electronic components, partners in WP3 had to face additional challenges.

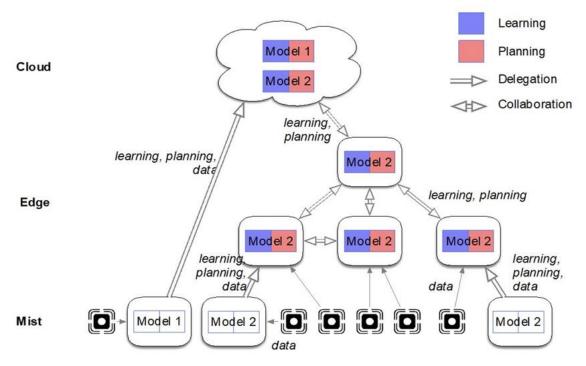

Figure 1 A schematic drawing of a possible FRACTAL system deployment using three different tiers of FRACTAL hardware nodes with different capabilities (drawing from WP5 technical meetings).

#### In the project the following options for the hardware nodes were used:

| V0.16 | Copyright © FRACTAL Project Consortium | 5 of 61 |

|-------|----------------------------------------|---------|

|       |                                        |         |

|         | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

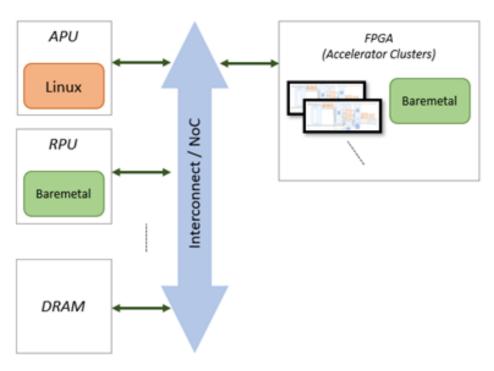

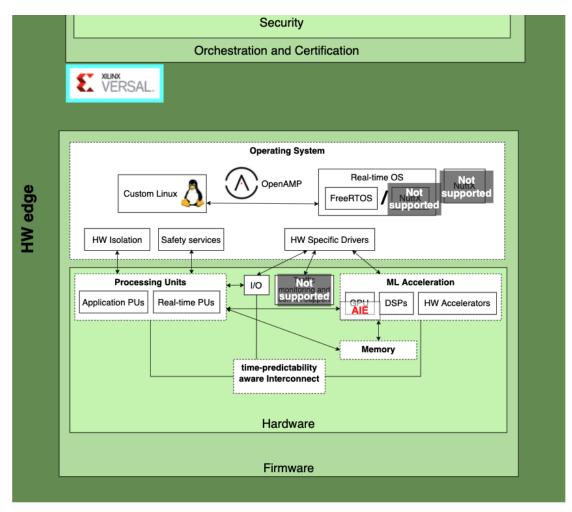

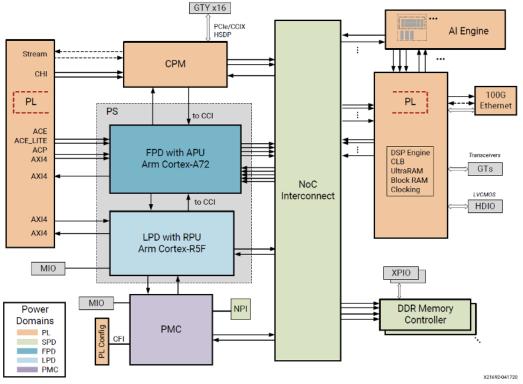

- 1. **Edge node** based around the Xilinx VERSAL ACAP (Adaptable Compute Acceleration Platform)

- 2. **Low-end node** (also as mist node) -- based around the open-source RISC-V based PULP platform

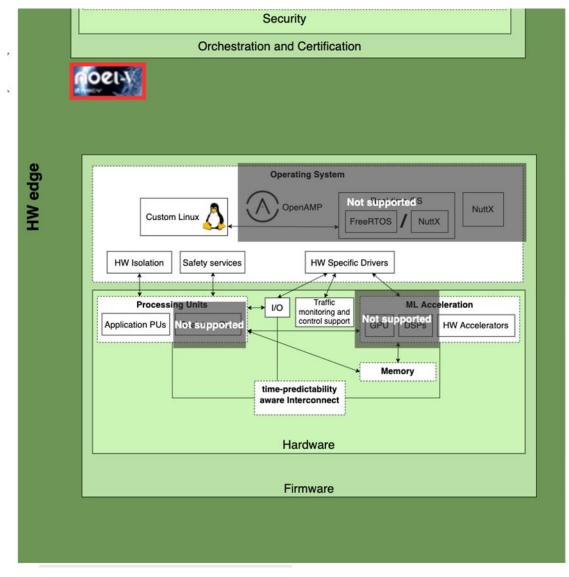

Additionally, some specific platforms (e.g., Ariane/CVA-6, NOEL-V) are used to demonstrate some specific technology concepts and use cases.

**Note**, in D3.2 also terms **customizable node** and **commercial node** were used. For now, on the Fractal domains are described by terms: **cloud**, **edge node** (Versal) and **low-end node** (Pulp). In case of cases where other platforms were used, their context will be clarified on text.

The organization of the deliverable is as follows.

Chapter 2 provides a general introduction to the Fractal framework and the stake holders using it. Chapter 3 summarizes WP3 technical relations to other WPs. Chapter 4 looks WP3 requirements for the Pulp platform point of view. Chapter 5 looks WP3 requirements for the Versal platform point of view. Chapter 6 introduces the special WP3 cases that were demonstrated by other platforms. Chapter 7 summaries and refers to the Fractal use cases.

| ALT-L   | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

# List of WP3 components

| nponent                                                        | (Sub)Con   | ponent / Development Name                             | Partner     | Deliv.       | Section |      |  |

|----------------------------------------------------------------|------------|-------------------------------------------------------|-------------|--------------|---------|------|--|

|                                                                |            |                                                       |             |              |         | <br> |  |

| 3-AI                                                           |            | rator (hardware and software                          |             |              |         |      |  |

| 3T32-01                                                        | Support)   | erator (SIEFRACC)                                     | SIEM        | D3.5         |         |      |  |

| 3T32-05                                                        |            | nce demo PULPissimo                                   | ETHZ        | D7.3         |         |      |  |

| 3T32-07                                                        |            | Gender identifier at the edge                         | UNIVAQ      | D3.5         |         |      |  |

| 3T32-10                                                        | -          | ccelerator building-blocks                            | IKER        | D3.5         | _       | <br> |  |

| 3T34-03                                                        |            | odel deployment layer                                 | PLC2        | D3.5         |         |      |  |

| 3T35-01                                                        | SW drive   | r for HW accelerator                                  | SIEM        | D3.6         | 2.2.6   |      |  |

| 3T35-02                                                        | Accelerat  | or Adaptation to AI library                           | UPV         | D3.5         |         |      |  |

| 3T35-03                                                        |            | w Energy EDDL)                                        | SML         | D3.6         | 2.2.2   |      |  |

| 3T35-04                                                        | Deen lea   | ning based automatic iris diagnosis                   | MODIS       | D3.6         | 22.2.1  |      |  |

| 4                                                              |            |                                                       |             |              |         |      |  |

| 3-                                                             |            |                                                       |             |              |         |      |  |

| J <del>/OS</del><br>3T32-02                                    |            | OS support<br>no platform for IoT applications        | FTH7        | D3 5         |         |      |  |

| 3T32-02<br>3T32-02b                                            |            | r Linux capable RISC-V platform                       | ETHZ        | D3.5         |         |      |  |

| 3T32-02D                                                       | PULP trai  |                                                       | ETHZ        | D3.5         |         |      |  |

| 3T32-04                                                        |            | port to PULP                                          | ETHZ        | D3.6         | 3.1.2   | <br> |  |

| 3T32-08                                                        |            | aware caches                                          | ACP         | D3.5         | 0.112   |      |  |

| 3T32-11                                                        |            | errupt distribution system                            | ACP         | D3.5         |         |      |  |

| 3T32-12                                                        |            | ervices - TL2AXI adapter                              | ACP         | D3.5         |         |      |  |

| 3T33-03                                                        | CVA6 (for  | mer Ariane) RISC-V core                               | THA         | D3.5         |         |      |  |

| 3T36-01                                                        | Linux for  | CVA6 (former Ariane)                                  | THA         | D3.6         | 33.2    | <br> |  |

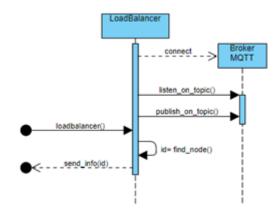

| 3T36-02                                                        | Load Bala  | incing Module                                         | MODIS       | D3.6         | 2.3.1.1 |      |  |

| 3T36-03                                                        | Nuttx on   |                                                       | OFFC        | D3.6         | 3.1     |      |  |

| 3-Safety                                                       | -          | d security features for CPU                           |             |              |         |      |  |

| 3T31-01                                                        | 0          | nted monitoring unit                                  | BSC         | D3.5         |         |      |  |

| 3T31-02                                                        |            | ect to support Accelerators                           | UPV         | D3.5         |         |      |  |

| 3131-02<br>3131-03                                             | integratio |                                                       | 10007       |              |         |      |  |

| 3131-03<br>3T32-06                                             |            | d security hardware support<br>ht Acceleration Scheme | UPV<br>LIPV | D3.5<br>D3.5 |         |      |  |

| р. Г.Э. С. – Г. (D)<br>- – – – – – – – – – – – – – – – – – – – |            | nr wrreisiannn orneille                               |             | 49.5         |         |      |  |

| 3T32-09                                                        |            | Bandwidth Regulator                                   | UNIVAQ      | D3.5         |         |      |  |

| 3134-01                                                        |            | the edge-oriented monitoring unit                     | BSC         | D3.6         | 2.2.4   |      |  |

| 3T34-02                                                        | Drivers fo | r the SW diverse redundancy library                   | BSC         | D3.6         | 2.2.3   |      |  |

|                                                                |            |                                                       |             |              | _       | <br> |  |

|                                                                |            |                                                       |             |              |         |      |  |

|                                                                |            |                                                       |             |              |         |      |  |

|                                                                |            |                                                       |             | -            |         |      |  |

|                                                                |            |                                                       |             |              |         |      |  |

Table 1 The FRACTAL components (according to D2.3) related to WP3. Some components will be described in D3.5 (and one in D7.3), for others the section in this deliverable is given

|         | Project FRACTAL: Cognitive Fractal and Secure Edge Based on Unique Open-Safe-Reliable-Low Power Hardware Platform Node | с                                       |

|---------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| FRACTAL | Title                                                                                                                  | Software node and services architecture |

| A THE A | Del. Code                                                                                                              | D3.6                                    |

### **1.1 Introduction**

FRACTAL is a system that offers a framework for developing modern distributed applications. Distributed applications can be executed in embedded nodes -- near the individual processes, centrally at the cloud, or as distributed into both of these domains. The supporting Framework should offer seamless connectivity, application integrity and the required security and safety. As addition the FRACTAL framework offers also an integrated AI tools also to the domains. Additionally, FRACTAL offers application specific hardware accelerations to the embedded nodes.

In the project proposal, we identified four strategic objectives of FRACTAL to reach this goal:

- **Objective 1**: Design and Implement an Open-Safe-Reliable Platform to Build Cognitive Edge Nodes of Variable Complexity. This part is mainly being addressed as part of WP3.

- **Objective 2**: Guarantee extra-functional properties (dependability, security, timeliness and energy-efficiency) of FRACTAL nodes and systems built using FRACTAL nodes (i.e., FRACTAL systems), which has determined the tasks of WP4

- **Objective 3**: Evaluate and validate the analytics approach by means of AI to help the identification of the largest set of working conditions still preserving safe and secure operational behaviors, which is the topic of WP5

- **Objective 4**: To integrate fractal communication and remote management features into FRACTAL nodes, which will be covered by WP6.

Looking outside, FRACTAL can be seen from various points of view. Most important are the end-user view and the application owner views.

### **1.2 Application owner view**

Applications are developed according to the developer's business logic. Initially the business owner will assume that on the market the application will offer an added value to the end customer(s). To benefit from this added value, business owners need strategies to enter the market and secondly keep and improve this position.

#### **1.2.1 Support for business logic**

Framework should offer freedom to implement various application scenarios according to their business opportunity. While the business case (market) develops the application developments should be easy to deploy.

Main purpose of FRACTAL framework is to minimize this work, without limiting too much the application developer freedom.

#### Fractal Use Cases described at D3.3, chapter 5.

|         | Project FRACTAL: Cognitive Fractal and Secure Edge Based on Uni<br>Open-Safe-Reliable-Low Power Hardware Platform Node | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title                                                                                                                  | Software node and services architecture                                                                           |

|         | Del. Code                                                                                                              | D3.6                                                                                                              |

#### 1.2.2 Support for development and testing

Framework should offer tools for actual development, testing and verification. Mainly these tools are "standard" development tools, but the Framework itself should have specific tools to identify (and prevent) unwanted behavior of application specific components.

While in some extreme cases embedded electronics are custom developed, in most cases the framework should offer seamless hardware acceleration.

Yet another important aspect of distributed applications is application integrity. All parts of the application must be consistent with each other. Framework should offer tools for safe application deployment and ensure that parts of the distributed application are genuine.

#### 1.2.3 Support for commissioning, deployment and provisioning

When the end-users are attracted by the business logic, the application is ramped to a specific end-user. This may require physical installations on site and/or configurations to the cloud. Application logic – by support of the framework – should distribute the configurations to end-user specific nodes.

Some cases there may be needs to collect end-user specific information – e.g., billing of further marketing needs – this information transfer must be secure.

#### **1.3 End-user view**

For the end-user (or the customers of the end-user) the distributed application integrates directly to their processes (**Fractal Use Cases described at D3.3, chapter 5**). Depending on the application, availability, operational safety, and information security are typically important aspects.

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

### 2 WP3 and related WPs

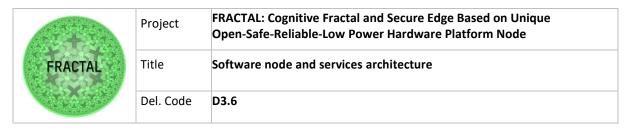

WP3 is focusing on the development of nodes – both the physical HWs and the necessary firmware. There are VERSAL based high-end nodes and low-end PULP based nodes. Both platforms have toolsets for application software and HW acceleration.

### 2.1 WP3 and WP4

The WP4 looks at the FRACTAL framework from point of safety -- how to manage physical defects on mechanics and electronics and the exceptional cases on software. Thus, these are highly related both to node hardware and node firmware, WP4 is deeply related to both WP3 nodes. Some exceptional cases are not necessarily possible to demonstrate on these platforms, so special platforms may be used.

#### 2.1.1 Supporting FRACTAL developments on safety

Today safety is mainly based on process and system assessments. As such, it is not a plain software feature, but more like process and documentation issue.

#### 2.1.2 Supporting FRACTAL developments on security

Two approaches are differentiated in the developments covering security related features.

#### 2.1.2.1 Linux based systems

Linux offers good tools for security. With HW support those can be strengthened to meet the requirements derived from specific use cases.

Additionally, for the VERSAL node (Linux based system as well), those use case applications that require device-level security could implement boot image encryption and authentication, functionalities that are natively supported by VERSAL.

#### 2.1.2.2 RTOS based systems

By nature, RTOS based systems have little native security features. With dedicated HW support those can be strengthened to meet the requirements, but in most cases security features are application specific implementations.

#### **2.1.3 Supporting FRACTAL developments on low power**

Two approaches are differentiated in the developments related to low consumption features.

#### 2.1.3.1 Linux based systems

Linux offers good tools for low power operations. For further needs the RTOS can be utilized. RTOS runs in additional processor or preferably one of the system cores. When low power requires Linux to switch itself off, it yields the responsibility to the RTOS. RTOS keeps processing events and, when defined conditions are met, it wakes up the Linux.

|         | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

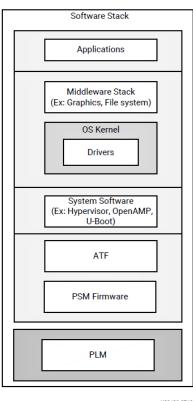

Additionally, for the VERSAL node (Linux based system as well), as shown in **iError! No se encuentra el origen de la referencia.** a centralized Platform Management Controller (PMC) that handles device management control functions is available. A flexible management control could be done through this PMC. This platform management handles several scenarios and allows the user to execute power management decisions through its framework (equivalent to what it is done in Linux, which provides basic power management capabilities like CPU frequency scaling).

However, some limitations apply. Because of the heterogeneous multi-core architecture of VERSAL, individual processors can't make autonomous decisions about power states of individual components or subsystems. Instead, a collaborative approach is taken, where a power management API delegates all power management control to the platform management controller. This PMC is the key component in coordinating the power management requests received from the other processing units, and the coordination and execution from other processing units through the power management API. This framework manages resources such as power domains, power islands, clocks, resets, pins and their relationship to CPU cores, memory, and peripheral devices.

Therefore, the natively provided power management API would be used for VERSAL node, since this platform management framework abstracts the complexity associated to administrate the power-management of a multiprocessor heterogeneous system.

#### 2.1.3.2 RTOS based systems

By nature, RTOS based systems offer good tools low-power operations. The RTOS level low-power features are typically extended with specific support by the underlying HW (processor).

Another additional layer of low power is typically obtained by application architecture. Event-based application structure is by nature easier for low-power than applications that are coded based on infinity loops, however this is not in scope of framework.

### 2.2 WP3 and WP5

WP5 focuses on integrating AI to the Fractal framework. While AI is in the scope of whole project, the WP3 has some special concerns related to implementation in the low resource environment.

#### 2.2.1 Supporting FRACTAL developments on AI

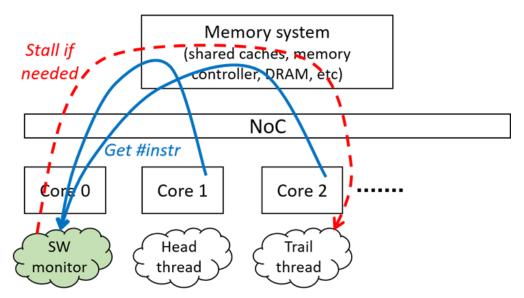

Several alternative methods are studied for deploying AI/ML models on FRACTAL nodes. First, a model may be pre-built, that is, trained by a third-party actor, downloaded from a public repository, and uploaded to the node. Second, a model may be learned from data available to a node, possibly augmented with annotations which indicate the expected model output for each data point. Third, a few nodes may co-operate to train a model, e.g., with a federated learning approach.

|         | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

In each case, the model may need updating due to model drift, that is, the accuracy of the model output slowly degrading. In such cases, new training data must be collected (and possibly annotated), and the model updated to reflect the data. Further, the model update cycle must be managed such that model quality is monitored and update launched when necessary. Tools and methods conducting model lifecycle management are commonly referred to as MLOps.

Inference-time, when the model is turning input data into model output, federated approaches may improve the quality of the outputs in some use cases. For example, if a number of nodes each employ an independently trained (i.e., with different data) but otherwise identical models, the models may be used as an ensemble, with the same input data fed to all of them, and the results combined into one.

WP5 is studying all above approaches in close co-operation with WP3, focusing on theoretical study of distributed learning and inference, the FRACTAL cloud platform, the architecture and orchestration of the FRACTAL network, as well as the AI methods required to fulfill the requirements of the use cases.

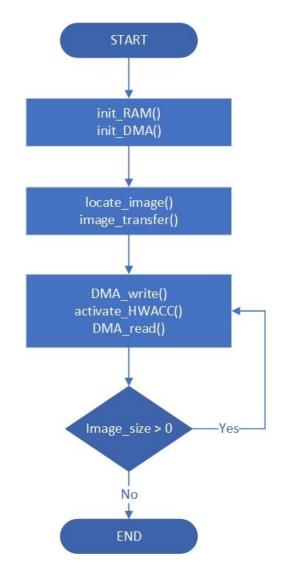

# 2.2.1.1 Raw imaging preprocessing requirements for IRIS disease detection (WP3T35-04)

To properly execute the classification algorithms for the monitoring and detection of diabetic retinopathy, three preprocessing techniques that proved to be the most effective in this field, had been chosen:

- 1. *Cropping*: a technique for bringing images to a square shape.

- 2. *Resize*: for bringing images with the same resolution.

- 3. *CLAHE*: advanced histogram equalization technique to improve the contrast of raw images.

Even though these techniques are well-known ones in literature, lately they are well implemented separately in a cloud environment within which, in a broad sense, there are no resources constraints. Our *new* approach is to use them all together in sequence in order to deploy the pre-processing *service* in a *commercial environment*, with resources limitations, to address specific research topics and to support the Fractal ecosystem.

These techniques are computationally expensive; therefore, it is necessary to study the limits, e.g., the minimum requirements, within which it is possible to run the preprocessing service avoiding the use of an oversized or undersized microprocessor board.

An evaluation of the average execution times was carried out to be able to evaluate the implemented Iris Recognition algorithm and be able to define the minimum hardware requirements to be able to run it correctly. This analysis was carried out on **a Zynq UltraScale + MPSoC ZCU102 board** using the entire IDRiD dataset (516 images).

The Zynq UltraScale + MPSoC ZCU102 board has the following features:

Quad-core Arm Cortex-A53 processor

-

|         | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

- CPU frequency up to 1.5GHz

- 4GB RAM Memory

To perform the evaluation, we made use of the *IDRiD dataset*. The IDRiD dataset (Indian Diabetic Retinopathy Image Dataset) contains fundus images that were captured by a retinal specialist containing 516 images. The size of each image is about 800 KB.

The preprocessing phase of an image consists, as mentioned before, of the operation of Crop, Resize, and Clahe.

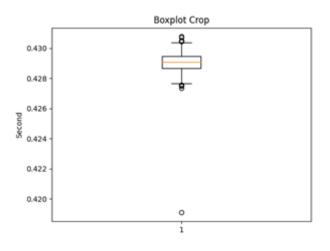

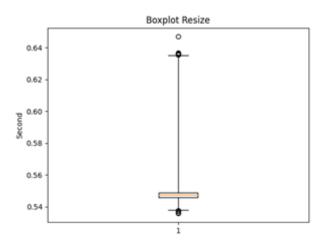

We found that the average execution times, evaluated on 4 Cores of the Cortex A53 processor, for the Crop, Resize, and Clahe operations are shown in the following table:

| Preprocessing<br>Phase | Averange Execution<br>time (s) | Number of<br>Core |

|------------------------|--------------------------------|-------------------|

| Crop                   | 0,550808249                    | 4                 |

| Resize                 | 0,429059386                    | 4                 |

| Clahe                  | 104,5466895                    | 4                 |

| Total Time (s)         | 105,5271729                    |                   |

Figure 2 Average execution time of Crop, Resize and Clahe algorithms on Zynq with 4-core running

The Crop operation required 0,550808249 s, the Resize operation required 0,429059386 s, and finally, the Clahe operation required 104,5466895 s. Therefore, the total average time for preprocessing phase is 105,5271729 s (1m 45s).

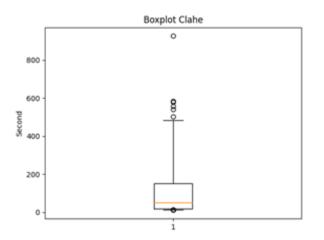

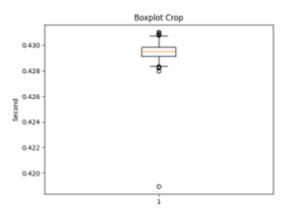

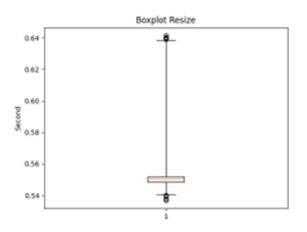

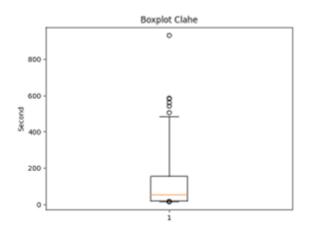

In detail, it was created a boxplot to display the summary of the set of data values having properties like a lower whisker, lower quartile, median, upper quartile, and upper whisker.

Figure 3 Boxplot for Crop Algorithm with 4-core running

|         | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

Figure 5 Boxplot for CLAHE Algorithm with 4-core running

| LABEL      | LOWER<br>WHISKER [s] | LOWER<br>QUARTILE [s] | MEDIAN [s] | UPPER<br>QUARTILE [s] | UPPER<br>WHISKER [s] |

|------------|----------------------|-----------------------|------------|-----------------------|----------------------|

| Box Crop   | 0.427664             | 0.428654              | 0.429077   | 0.429022              | 0.430383             |

| Box Resize | 0.537745             | 0.545758              | 0.547378   | 0.547167              | 0.635081             |

| Box CLAHE  | 12.438491            | 16.811439             | 50.663041  | 41.275369             | 483.239338           |

Table 2 Statistical insights for algorithms running with 4-core.

The subsequent study has been conducted calculating the average execution times, with only 1 Core of the Cortex A53 running, for the Crop, Resize, and Clahe.

| V0.16 | Copyright © FRACTAL Project Consortium | 14 of 61 |

|-------|----------------------------------------|----------|

| 10.10 |                                        | 14 01 01 |

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

| Preprocessing<br>Phase | Averange Execution<br>time (s) | Number of<br>Core |

|------------------------|--------------------------------|-------------------|

| Crop                   | 0,55360711                     | 1                 |

| Resize                 | 0,429484704                    | 1                 |

| Clahe                  | 108,0786817                    | 1                 |

| Total Time (s)         | 109,0623796                    |                   |

Figure 6 Average execution time of Crop, Resize and Clahe algorithms on Zynq with 1-core running

The Crop operation required 0,55360711 s, the Resize operation required 0,429484704 s, and finally, the Clahe operation required 108,0786817 s. Therefore, the total average time for preprocessing phase is 109,0623796 s (1m 49s).

Figure 7 Boxplot for Crop Algorithm with 1-core running

Figure 8 Boxplot for Resize algorithm with 1-core running

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

Figure 9 Boxplot for CLAHE algorithm with 1-core running

| LABEL      | LOWER<br>WHISKER [s] | LOWER<br>QUARTILE [s] | MEDIAN [s] | UPPER<br>QUARTILE [s] | UPPER<br>WHISKER [s] |

|------------|----------------------|-----------------------|------------|-----------------------|----------------------|

| Box Crop   | 0.428366             | 0.429135              | 0.429511   | 0.429462              | 0.430748             |

| Box Resize | 0.540493             | 0.548339              | 0.550389   | 0.550140              | 0.638475             |

| Box CLAHE  | 16.173421            | 20.232431             | 54.147033  | 44.750463             | 486.486875           |

Table 3 Statistical insights for algorithms running on 1-core processor.

Another step studying the minimum hardware required was on the variation of the RAM memory and the number of the Cores of the Cortex A53 processor made available for the image preprocessing operation. The following table shows the results of the evaluation with the variation of RAM and with 4 Cores of the Cortex A-53 processor.

| RAM Memory Used<br>with 4 CPU core | Result                                                             | Number of Image pre-<br>processed sequentially |

|------------------------------------|--------------------------------------------------------------------|------------------------------------------------|

| 300 Mbyte                          | Insufficient RAM memory                                            | 1                                              |

| 400 Mbyte                          | Insufficient RAM memory                                            | 1                                              |

| 500 Mbyte                          | Insufficient RAM memory                                            | 1                                              |

| 600 Mbyte                          | Crop error, overload resolution<br>failed, insufficient RAM memory | 1                                              |

| 700 Mbyte                          | Pre-Processing executed                                            | 1                                              |

| 700 Mbyte                          | Insufficient RAM memory                                            | 2                                              |

| 800 Mbyte                          | Insufficient RAM memory                                            | 2                                              |

| 900 Mbyte                          | Insufficient RAM memory                                            | 2                                              |

| 1 GByte                            | Pre-Processing executed                                            | 2                                              |

| 1 Gbyte                            | Pre-Processing executed                                            | 2+                                             |

Table 4 Minimum RAM memory required if 4-core running

It is noteworthy how we obtained different results increasing RAM memory and number of images to be processed. In particular:

- For only one image to be processed 700MB of RAM is enough.

| V0.16 | Copyright © FRACTAL Project Consortium | 16 of 61 |

|-------|----------------------------------------|----------|

|       |                                        |          |

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

- For two or more images to be processed sequentially it needs 1GB RAM.

The following table shows the results of the evaluation with the variation of RAM and with 4 Cores of the Cortex A-53 processor.

| RAM Memory Used<br>with 1 CPU core | Result                  | Number of Image pre-<br>processed sequentially |  |

|------------------------------------|-------------------------|------------------------------------------------|--|

| 300 Mbyte                          | Insufficient RAM memory | 1                                              |  |

| 400 Mbyte                          | Insufficient RAM memory | 1                                              |  |

| 500 Mbyte                          | Pre-Processing executed | 1                                              |  |

| 500 Mbyte                          | Insufficient RAM memory | 2                                              |  |

| 600 Mbyte                          | Pre-Processing executed | 2                                              |  |

| 600 Mbyte                          | Pre-Processing executed | 2+                                             |  |

Table 5 Minimum RAM memory required if 1-core running

It is possible to notice how we obtained different results as it increases RAM memory and the number of images to be processed. In particular:

- For only one image to be processed 500MB of RAM is enough.

- For two or more images to be processed sequentially it needs 600MB RAM.

From this evaluation, it comes out that the minimum requirements for preprocessing a large image dataset with Crop, Resize and CLAHE algorithms are listed in the following table:

| Number of cores required           | RAM memory |

|------------------------------------|------------|

| 1 Core                             | 1GB        |

| Cortex A-53 processor (or similar) |            |

In order to provide full operability and access to these features to any application, we arranged the algorithms in a docker service. It can be executed from any application with the following command:

• docker run modis\_irisrecognition\_app

The logic underneath is pretty simple, taking an image as input, processing sequentially this raw image with Crop, Resize and Clahe algorithm and produce a preprocessed image as output.

#### 2.2.2 LEDEL to develop and execute AI-based models in a FRACTAL node

The aim of this work is to port EDDL to be used in a RISCV architecture, so machine learning algorithms can be executed in such hardware.

There has been attempts to extend the RISC-V Instruction Set Architecture with the goal of accelerating the inference process of CNN. In this attempts a new processor, extending an already existing processor with the new set of instructions, was built into an FPGA,

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

where its performance was tested showing a x2 performance improvement using TensorFlow Lite models [<u>https://ieeexplore.ieee.org/abstract/document/9071197</u>].

Another work extending the instruction set of RISC-V architecture to allow TensorFlow Lite cross-compilation and execution [https://www.researchgate.net/publication /339298701\_Towards\_Deep\_Learning\_using\_TensorFlow\_Lite\_on\_RISC-V].

During the RISC-V Summit of 2019, LG presented the LG Neural Engine (LNE), a processor with customized ISA extensions of RISC-V to support neural network functions. The LNE software framework can support the inference of trained models in Caffe, TensorFlow and PyTorch [https://riscv.org/wp-content/uploads/2019/12/12.10-15.50a-Scalable-Configurable-Neural-Network-Accelerator-Based-on-RISC-V-Core.pdf].

Another interesting work a Neural Network framework base on the RISC-V architecture is develop, achieving the execution of lightweight models with accuracy results like the same models run using Keras [https://link.springer.com/chapter/10.1007/978-3-030-49556-5\_8].

#### 2.2.2.1 LEDEL in the FRACTAL project

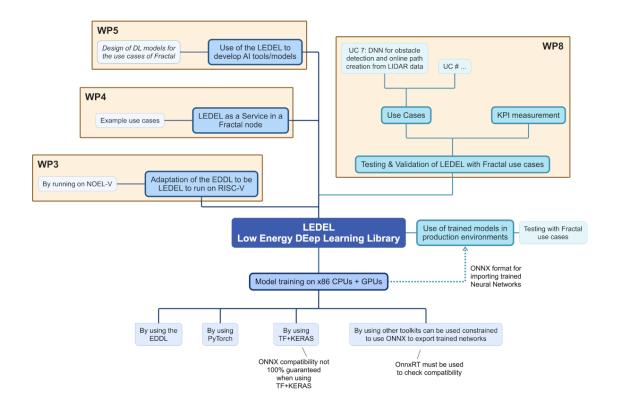

In Figure 10 LEDEL development in FRACTAL we can observe the scope of the task in WP3 in the context of LEDEL in the FRACTAL project, which is the adaptation of the EDDL to become LEDEL. Such adaptation consists of compiling the EDDL in a RISC-V platform, reassuring all the libraries and dependencies that it needs are also available and fully functional in the reduced instruction set architecture. The platform chosen for this aim is NOEL-V. This platform is scheduled to be available before the end of the year.

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

Figure 10 LEDEL development in FRACTAL

Thus, in order to check that the LEDEL could be ported to this hardware, we have used an emulated environment for the RISC-V architecture based on QEMU software. For this purpose, we have used an already created and compiled Linux Debian image named "Artifacts"

https://gitlab.com/api/v4/projects/giomasce%2Fdqib/jobs/artifacts/master/download?job=con vert\_riscv64-virt

from the project repository

https://gitlab.com/giomasce/dgib#debian-guick-image-baker-dgib

Once the image has been installed and running, EDDL has been compiled in this RISC-V virtualized environment. All the dependencies work completely fine. And a few simple tests have been executed checking their proper behavior.

One can train a model using the EDDL on a computer without limitation of resources and export it using the ONNX format. Afterwards, the model can be imported by the LEDEL in a FRACTAL node, and then used to infer from data received in the node.

As an example, it has been possible to train a simple model for the MNIST digit dataset, and then use it for inference. Obviously, as all infrastructure is being emulated, this execution process has been quite slow. Also, it has been possible (i) to train this model

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

using an "outside" computer, (ii) to save it in ONNX format, (iii) to import it in the emulated machine and (iv) to infer.

The use of this pre-baked image of Linux running on RISC-V emulated platform has allowed us to check if the portability of the EDDL to this architecture was possible. Furthermore, it has given us the advantage of moving forward with T4.1 (LEDEL as a service in a FRACTAL node), and now we are able to test the deep learning model for the UC7.

This intermediate solution has been documented and packed using a docker and is available in the repository of the FRACTAL project: [https://github.com/project-fractal/WP3/tree/main/Components/WP3T35-03%20LEDEL].

#### 2.2.2.2 Presentation and preparation of the emulated NOEL-V platform

We have used the software named isar-riscv provided by our partner Siemens in <a href="https://github.com/siemens/isar-riscv/blob/main/README.md">https://github.com/siemens/isar-riscv/blob/main/README.md</a>.

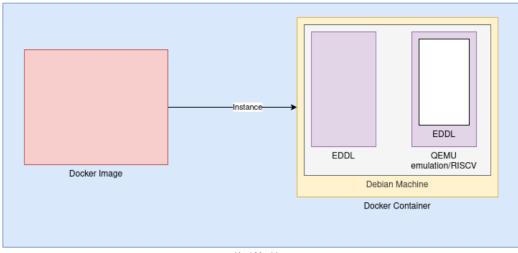

The requirements of such software need to be installed and deployed in a Debian Linux System. To this aim, a docker container with the Debian GNU/Linux 11 distribution has been prepared. In it the isar-riscv solution has been deployed, following the instructions from the official repository.

We have also prepared a manual in a more detailed manner to prepare all the infrastructure needed to use the LEDEL, as well as to instruct how one can install and use the library to create ML algorithms in the FRACTAL node [https://github.com/project-fractal/WP3/tree/main/Components/WP3T35-03%20LEDEL]. We basically have followed the official documentation with the addition of a couple of extra steps for a better and friendlier performance. It should be noted that we can custom upgrade the docker file to our taste or necessities.

Since the EDDL installation is already explained in the official documentation and, also, in the user manual, in this document we will focus on how the LEDEL works in a RISCV based architecture machine, emulated in this case. Due to the fact that we have reduced space, the simplest and safest way to achieve this goal is to download the original code of the

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

library and compile it. As said before, all steps are well documented in FRACTAL project Github repository.

Host Machine

Figure 11 Abstraction of the docker file presented

Finally, Figure 11 Abstraction of the docker file presented, shows the content of the docker container created to mount the LEDEL infrastructure. We have installed the EDDL library to write and compile algorithms using it. Later, they can be exported using ONNX and transferred to the FRACTAL node. In this case, the QEMU emulation of RISC-V acts as the FRACTAL node. After creating the ONNX model, the file created is imported inside the RISC-V emulation to be tested and executed correctly using a network loader implemented with what is already LEDEL. We will refer to the emulation process as the FRACTAL node since it is the exact same process to follow once the FRACTAL node hardware is available.

The steps followed to achieve this are related in more detail below. Basically, we have trained two simple models using two different technologies. The first one is implemented using EDDL library. It consists of a simple neural network implementation that trains using the MNIST dataset. Code used to illustrate this example can be accessed following the link: <a href="https://deephealthproject.github.io/eddl/usage/intermediate.html">https://deephealthproject.github.io/eddl/usage/intermediate.html</a>

After the training, the ONNX file is created with the weights in a .bin file. We can observe in Figure 12 Example of training process using LEDEL in RISCV, the results of the training process.

| FRACTAL | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

|         | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

|                |            | _examples/mnist                         | _eddl_tr | ain/builo | d\$ ./mnist_ed            | ldl_train                                  |

|----------------|------------|-----------------------------------------|----------|-----------|---------------------------|--------------------------------------------|

| Downloading mr |            |                                         |          |           |                           |                                            |

| mnist_trX.bin  |            | o/ F                                    |          |           | 0 (0)00/-                 | 1- 40-                                     |

| mnist_trX.bin  |            | %[============                          | =====>]  | 179.44M   | 9.63MB/s                  | in 18s                                     |

| mnist_trY.bin  |            | o. F                                    |          |           | 10 0101                   |                                            |

| mnist_trY.bin  |            | %[===================================== | =====>]  | 2.29M     | 10.2MB/s                  | in 0.2s                                    |

| mnist_tsX.bin  |            |                                         |          | ~~ ~~     |                           |                                            |

| mnist_tsX.bin  |            | %[===================================== | =====>]  | 29.91M    | 10.5MB/s                  | in 2.8s                                    |

| mnist_tsY.bin  |            | o/ F                                    |          | 200 644   | 101-                      | 1- 0.05-                                   |

| mnist_tsY.bin  |            | %[===========                           | =====>]  | 390.64K   | KB/S                      | in 0.05s                                   |

| Generating Ran |            |                                         |          |           |                           |                                            |

| sh: 1: dot: no |            | - <b>C</b> -11                          |          |           |                           |                                            |

|                |            | e following com                         |          |           |                           |                                            |

|                |            | /tmp.dot >./mod                         | el.pdf   |           |                           |                                            |

| CS with full r |            | up                                      |          |           |                           |                                            |

| Building model | ι          |                                         |          |           |                           |                                            |

| model          |            |                                         |          |           |                           |                                            |

|                |            |                                         |          |           |                           |                                            |

| input1         | (784)      | =>                                      | (784)    |           | O                         |                                            |

| dense1         | (784)      | =>                                      | (1024)   |           | 803840                    |                                            |

| leaky_relu1    | (1024)     | =>                                      | (1024)   |           | 0                         |                                            |

| dense2         | (1024)     | =>                                      | (1024)   |           | 1049600                   |                                            |

| leaky relu2    |            | =>                                      | (1024)   |           | 0                         |                                            |

| dense3         | (1024)     | =>                                      | (1024)   |           | 1049600                   |                                            |

| leaky_relu3    | (1024)     | =>                                      | (1024)   |           | Θ                         |                                            |

| dense4         | (1024)     | =>                                      | (10)     |           | 10250                     |                                            |

| softmax4       | (10)       | =>                                      | (10)     |           | O                         |                                            |

|                |            |                                         |          |           |                           |                                            |

| Total params:  |            |                                         |          |           |                           |                                            |

| Trainable para |            |                                         |          |           |                           |                                            |

| Non-trainable  | params: 0  |                                         |          |           |                           |                                            |

| 4              |            |                                         |          |           |                           |                                            |

| 1 epochs of 60 | ou batches | of size 100                             |          |           |                           |                                            |

| Epoch 1        |            |                                         |          | 1 (1      | 00 <b>f</b> + <b>4[</b> ] |                                            |

| 4570 7044      | - (        |                                         |          | ] 60      | 90 SOTTMax4[l             | loss=0.888 metric=0.696] 2.6212 secs/batch |

| 1572.7344 secs | s/epocn    |                                         |          |           |                           |                                            |

Figure 12 Example of training process using LEDEL in RISCV

Now, we can import the ONNX file into the LEDEL and use the following code to load the trained network Figure 13 Code used to load the ONNX file using the LEDEL.

| ++++++++ | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL  | Title     | Software node and services architecture                                                                           |

|          | Del. Code | D3.6                                                                                                              |

```

#include <cstdio>

#include <cstdlib>

#include <iostream>

#include "eddl/apis/eddl.h"

#include "eddl/serialization/onnx/eddl_onnx.h"

using namespace eddl;

int main(int argc, char **argv) {

// Load dataset

Tensor* x_test = Tensor::load("mnist_tsX.bin");

Tensor* y_test = Tensor::load("mnist_tsY.bin");

// Preprocessing

x_test->div_(255.0f);

// Load net

Net* net = import_net_from_onnx_file("mlp_mnist.onnx");

// Build model

build(net,

rmsprop(0.01), // Optimizer

{"soft_cross_entropy"}, // Losses

{"categorical_accuracy"}, // Metrics

//CS_GPU({1}) // one GPU

//CS_GPU({1,1},100) // two GPU with weight sync every 100 batches

CS_CPU(),

//CS_FPGA({1})

false //Disable model initialization, since we want to use the onnx

//weights

);

// View model

summary(net);

// Evaluate

evaluate(net, {x_test}, {y_test});

}

```

Figure 13 Code used to load the ONNX file using the LEDEL

|         | Project   | FRACTAL: Cognitive Fractal and Secure Edge Based on Unique<br>Open-Safe-Reliable-Low Power Hardware Platform Node |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| FRACTAL | Title     | Software node and services architecture                                                                           |

|         | Del. Code | D3.6                                                                                                              |

It will be imported as ONNX into the FRACTAL node, loaded into the LEDEL so we can perform the inference part of the machine learning algorithm. We can see the results in Figure 14 Inference from ONNX file:

| <pre>garcia@nlp:~/Desktop/Proyectos/Fractal/ejemplo_eddl/mnist_mlp_import/build\$ ./mnist_mlp_import enerating Random Table S with full memory setup uilding model without initialization</pre> |                            |                                                    |                                                                                             |                                                                |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------|-----------|

| nodel                                                                                                                                                                                           |                            |                                                    |                                                                                             |                                                                |           |

| .nput1  <br>lense1  <br>.eaky_relu1 <br>lense2  <br>.eaky_relu2 <br>lense3  <br>.eaky_relu3 <br>lense4  <br>softmax4                                                                            | (1024)<br>(1024)<br>(1024) | =><br>=><br>=><br>=><br>=><br>=><br>=><br>=><br>=> | (784)<br>(1024)<br>(1024)<br>(1024)<br>(1024)<br>(1024)<br>(1024)<br>(1024)<br>(10)<br>(10) | 0<br>803840<br>0<br>1049600<br>0<br>1049600<br>0<br>10250<br>0 |           |

| lon-trainable                                                                                                                                                                                   | ams: 2913290               |                                                    |                                                                                             | ] 1000 softmax4[loss=0.265_metr                                | Lc=0.931] |

Figure 14 Inference from ONNX file

The second example shows a similar process, but the only difference is that we have implemented the training phase using PyTorch framework, imported the model into an ONNX file and then, the network is loaded using a similar program to the one showed before, can be seen in Figure 15 PyTorch example execution:

| => (28, 28) | 0                                   |

|-------------|-------------------------------------|

|             |                                     |

| => (784)    | 0                                   |

| => (1024)   | 803840                              |

| => (1024)   | 0                                   |

| => (1024)   | 1049600                             |

| => (1024)   | 0                                   |

| => (10)     | 10250                               |

|             | => (1024)<br>=> (1024)<br>=> (1024) |

Figure 15 PyTorch example execution

Apart from these two basic examples, we have also proven that the tools for crosscompiling for RISC-V architecture. Then, we can load the cross-compiled file into the FRACTAL node (in our case, the emulated RISC-V environment inside the docker container dedicated to this example).

| V0.16 | Copyright © FRACTAL Project Consortium | 24 of 61 |

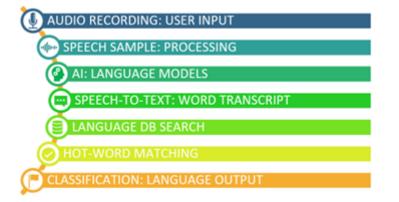

|-------|----------------------------------------|----------|